8399

8399

N/B Maintenance

N/B Maintenance

75

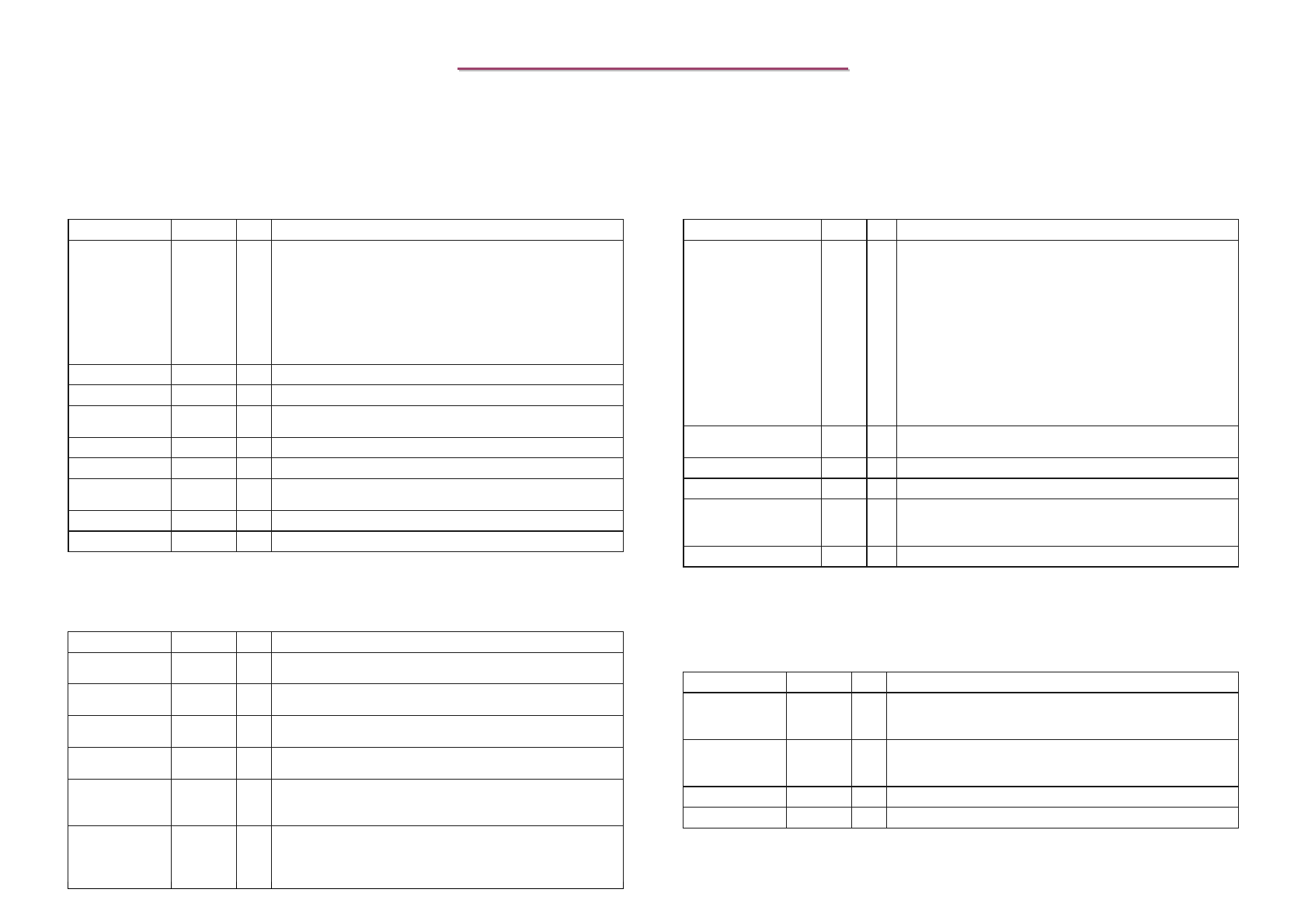

V-Link Interface

Signal Name Pin # I/O Signal Description

VAD7,

VAD6,

VAD5,

VAD4,

VAD3,

VAD2,

VAD1,

VAD0

AF25

AD24

AF20

AE19

AE24

AF24

AD21

AD20

IO

IO

IO

IO

IO

IO

IO

IO

Address / Data Bus. Also used to pass strap information from

the South Bridge to the North Bridge (the actual straps are on

the indicated South Bridge pin and that information is passed to

the North Bridge at reset time via the VAD pins).

VPAR

AF19 IO

Parity.

VBE#

AE21 IO

Byte Enable.

UPCMD

AF26 I

Command from Client (South Bridge) to Host (North

Bridge).

UPSTB

AE23 I

Strobe from Client to Host.

UPSTB#

AF23 I

Complement Strobe from Client to Host.

DNCMD

AD23 O

Command from Host (North Bridge) to Client (South

Bridge).

DNSTB

AF22 O

Strobe from Host to Client.

DNSTB#

AD22 O

Complement Strobe from Host to Client.

CRT Interface

Signal Name Pin # I/O Signal Description

AR

AG

AB

B3

A3

A2

AO

AO

AO

Analog Red. Red output to CRT monitor.

Analog Green. Green output to CRT monitor.

Analog Blue. Blue output to CRT monitor.

RSET

C4 AI CRT Output Reference Resistor. Tie to GNDRGB through an

external 90.9 ±1% resistor to

control the "RGB" RAMDAC full-scale current.

HSYNC

A1 O Horizontal Sync. Digital output to CRT monitor.

VSYNC

B1 O Vertical Sync. Digital output to CRT monitor.

SMB / I 2 C Interface

Signal Name Pin # I/O Signal Description

SBPLCLK /

GIRDY

AC10 I/O

I 2 C Serial Bus Clock for Panel (Muxed on AGP Bus Pins).

SBPLDAT /

GC#BE1

AF11 I/O

I 2 C Serial Bus Data for Panel (Muxed on AGP Bus Pins).

SBDDCCLK /

GREQ

Y1 I/O

I 2 C Serial Bus Clock for CRT DDC (Muxed on AGP Bus

Pins).

SBDDCDAT /

GGNT

AA3 I/O

I 2 C Serial Bus Data for CRT DDC (Muxed on AGP Bus

Pins).

SPCLK[2:1]

C2, P2 IO Serial Port (SMB/I 2 C) Clocks. Clocks for serial data transfer.

SPCLK1 is typically used for I 2 C communications. SPCLK2

is typically used for CRT Display DDC communications.

SPDAT[2:1]

C1, P1 IO Serial Port (SMB/I 2 C) Data. Data signals for serial data

transfer. SPDAT1 is typically used for I 2 C communications.

SPDAT2 is typically used for CRT Display DDC

communications.

Dedicated Digital Video Port 0 (DVP0) – TMDS Interface

Signal Name Pin # I/O Signal Description

DVP0D11/ TVD11

DVP0D10/ TVD10

DVP0D9 / TVD9

DVP0D8 / TVD8

DVP0D7 / TVD7

DVP0D6 / TVD6

DVP0D5 / TVD5

DVP0D4 / TVD4

DVP0D3 / TVD3

DVP0D2 / TVD2

DVP0D1 / TVD1

DVP0D0 / TVD0

M1

M3

M2

L1

M4

L3

L2

K1

L4

K3

K2

J1

O Digital Video Port 0 Data. Default output drive is 8 mA. 16

mA may be selected via SR3D[6]=1.

NOTE: DVP0D[6:0] are also used for power-up reset straps

for the embedded graphics controller. Check the Strap Pin

table for details.

DVP0HS / TVHS N4 O Digital Video Port 0 Horizontal Sync. Internally pulled

down.

DVP0VS / TVVS N3 O Digital Video Port 0 Vertical Sync. Internally pulled down.

DVP0DE / TVDE N1 O Digital Video Port 0 Data Enable. Internally pulled down.

DVP0DET / TVCLKR P4 I Digital Video Port 0 Display Detect. If VGA register

3C5.12[5]=0, 3C5.1A[5] will read 1 if display is connected.

Tie to GND if not used.

DVP0CLK / TVCLK P3 O Digital Video Port 0 Clock. Internally pulled down.

The terminology ie3C5.nnlg above refers to the VGA iGSequencerl. registers at I/O port 3C5 index

“nn”

5.2 VIA K8N800 North Bridge(3)

MiTac Secret

Confidential Document