8399

8399

N/B Maintenance

N/B Maintenance

82

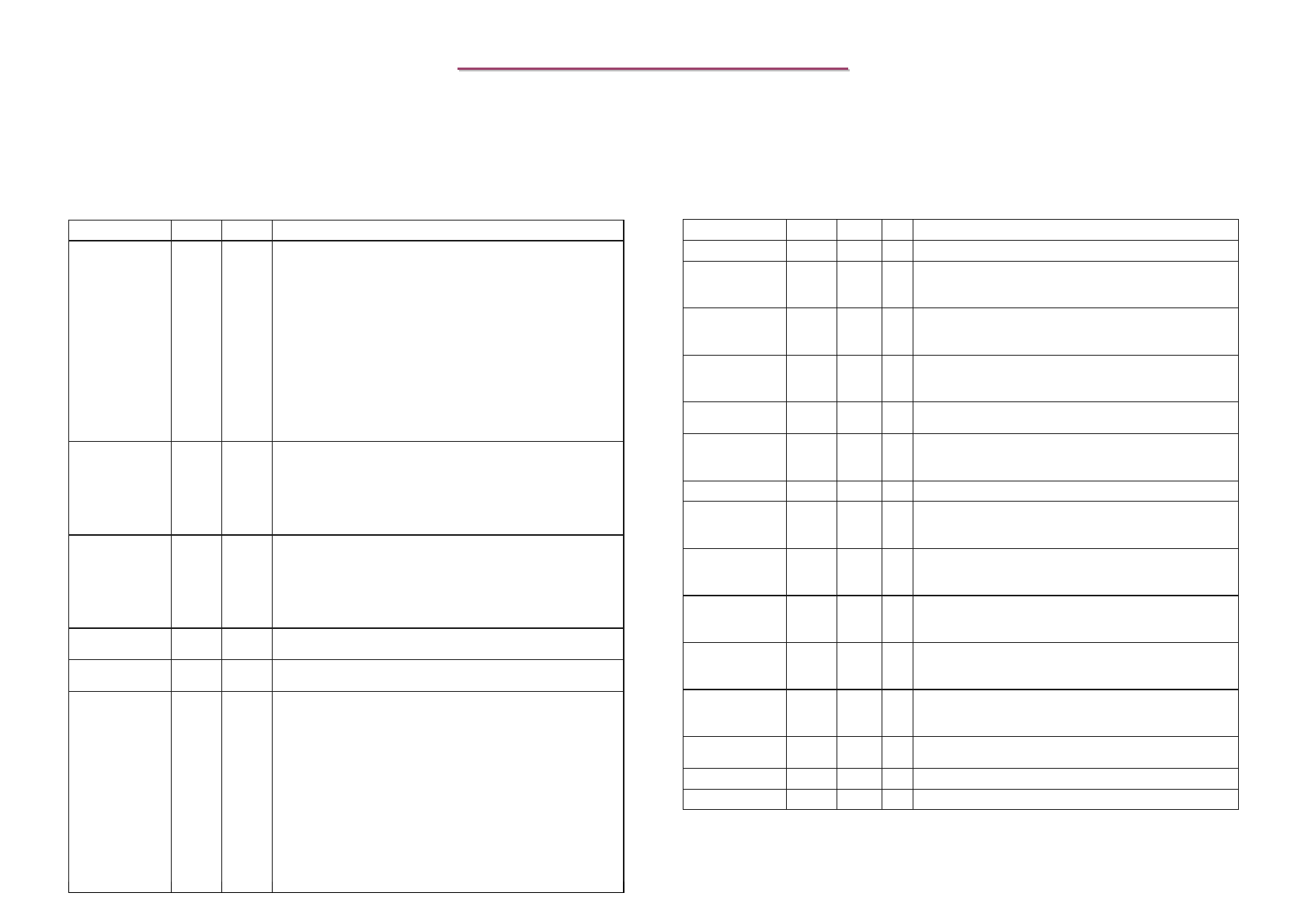

PCI Bus Interface (Continued)

Signal Name Pin # I/O Signal Description

INTA#

INTB#

INTC#

INTD#

INTE# / GPI12, /

GPO12,

INTF#

/ GPI13, /

GPO13,

INTG# / GPI14, /

GPO14,

INTH# / GPI15, /

GPO15

A4

B4

B5

C4

D4

E4

A3

B3

I PCI Interrupt Request. The INTA# through INTD# pins are

typically connected to thePCI bus INTA#-INTD# pins per the

table below. INTE-H# are enabled by setting Device17,

Function 0 Rx5B[1] = 1. BIOS settings must match the physical

connection method.

INTA# INTB# INTC# INTD#

PCI Slot 1 INTA# NTB# INTC# INTD#

PCI Slot 2 INTB# INTC# INTD# INTE#

PCI Slot 3 INTC# INTD# INTE# INTF#

PCI Slot 4 INTD# INTE# INTF# INTG#

PCI Slot 5 INTE# INTF# INTG# INTH#

PCI Slot 6 INTF# INTG# INTH# INTA#

REQ5#

/ GPI7,

REQ4#,

REQ3#,

REQ2#,

REQ1#,

REQ0#

R3

P3

D5

C5

B6

A5

I

PCI Request.

These signals connect to the VT8235 Version CE

from each PCI slot (oreach PCI master) to request the PCI bus.

To use pin R3 as REQ5#, Function 0 RxE4 mustbe set to 1

otherwise this pin will function as General Purpose Input 7.

GNT5# / GPO7,

GNT4#,

GNT3#,

GNT2#,

GNT1#,

GNT0#

R2

R4

E5

C6

D6

A6

O PCI Grant. These signals are driven by the VT8235 Version

CE to grant PCI access to aspecific PCI master. To use pin R2

as GNT5#, Function 0 RxE4 must be set to 1otherwise this pin

will function as General Purpose Output 7.

PCIRST#

R1 O PCI Reset. This signal is used to reset devices attached to the

PCI bus.

PCICLK

R23 I PCI Clock. This signal provides timing for all transactions on

the PCI Bus.

PCKRUN#

AB7 IO PCI Bus Clock Run. This signal indicates whether the PCI

clock is or will be stopped

(high) or running (low). The VT8235 Version CE drives this

signal low when the PCI

clock is running (default on reset) and releases it when it stops

the PCI clock. External

devices may assert this signal low to request that the PCI clock

be restarted or prevent it

from stopping. Connect this pin to ground using a 100 §Ù

resistor if the function is not

used. Refer to the ihPCI Mobile Design Guidelo and applicable

VIA North Bridge Design

Guide (KT400A, CLE266, or P4X400) for more details.

LAN Controller - Media Independent Interface (MII)

Signal Name Pin # I/O PU Signal Description

MCOL

B11 I

PD

MII Collision Detect. From the external PHY.

MCRS

A11 I

PD

MII Carrier Sense. Asserted by the external PHY when

the media is

active.

MDCK

A7 O

PD

MII Management Data Clock. Sent to the external PHY

as a timing

reference for MDIO

MDIO

B7 IO

PD

MII Management Data I/O. Read from the MDI bit or

written to the

MDO bit.

MRXCLK

C9 I

PD

MII Receive Clock. 2.5 or 25 MHz clock recovered by the

PHY.

MRXD[3-0]

C7, A8,

B8, C8

I

PD

MII Receive Data. Parallel receive data lines driven by the

external

PHY synchronous with MRXCLK.

MRXDV

D8 I

PD

MII Receive Data Valid.

MRXERR

D10 I

PD

MII Receive Error. Asserted by the PHY when it detects a

data

decoding error.

MTXCLK

C10 I

PD

MII Transmit Clock.

Always active 2.5 or 25 MHz clock

supplied by

the PHY.

MTXD[3-0]

A9, B9,

B10,

A10

O

PD

MII Transmit Data. Parallel transmit data lines

synchronized to

MTXCLK.

MTXENA

C11 O

PD

MII Transmit Enable. Signals that transmit is active from

the MII

port to the PHY.

MIIVCC

D9, E9,

E10,

E11

Power

MII Interface Power. 3.3V ±5%.

MIIVCC25

D12,

E12

Power

MII Suspend Power. 2.5V ±5%.

RAMVCC

E7

Power

Power For Internal LAN RAM. 2.5V ±5%.

RAMGND

E6

Power

Ground For Internal LAN RAM.

5.3 VIA VT8235CD South Bridge(3)

MiTac Secret

Confidential Document