8399

8399

N/B Maintenance

N/B Maintenance

76

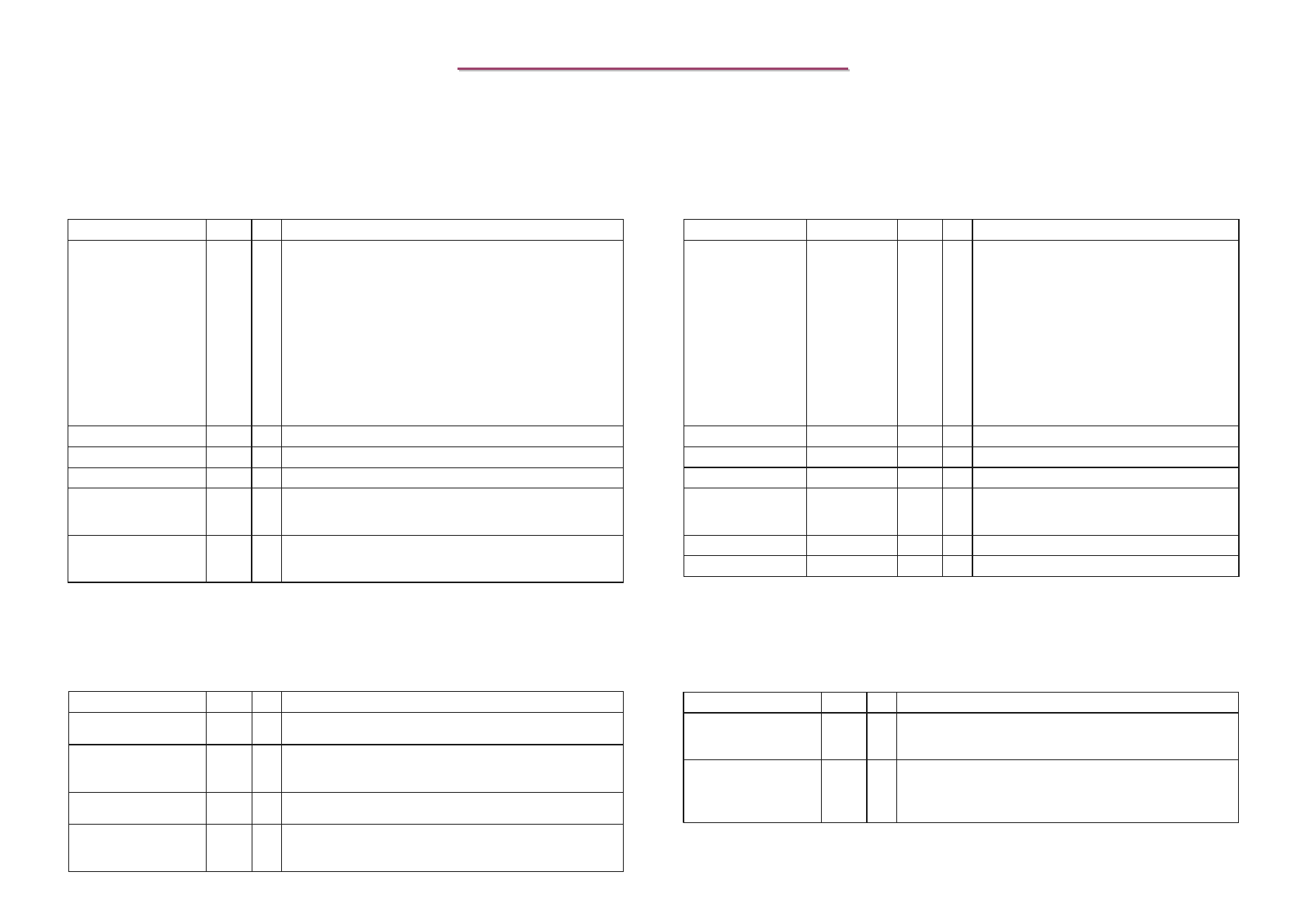

Dedicated Digital Video Port 0 (DVP0) - TV Encoder Interface

Signal Name Pin # I/O Signal Description

TVD11 / DVP0D11

TVD10 / DVP0D10

TVD9 / DVP0D9

TVD8 / DVP0D8

TVD7 / DVP0D7

TVD6 / DVP0D6

TVD5 / DVP0D5

TVD4 / DVP0D4

TVD3 / DVP0D3

TVD2 / DVP0D2

TVD1 / DVP0D1

TVD0

/ DVP0D0

M1

M3

M2

L1

M4

L3

L2

K1

L4

K3

K2

J1

O

TV Encoder 0 Data.

To configure DVP0 as a TV Out interface port, pins

DVP0D[6:5] must be strapped high.

Note: One TV Encoder interface is supported through either

DVP0 or GDVP1.

TVHS / DVP0HS N4 O TV Encoder 0 Horizontal Sync. Internally pulled down.

TVVS / DVP0VS N3 O TV Encoder 0 Vertical Sync. Internally pulled down.

TVDE / DVP0DE N1 O TV Encoder 0 Display Enable. Internally pulled down.

TVCLKR / DVP0DET P4 I TV Encoder 0 Clock Return. Input from TV encoder.

Internally pulled

down.

TVCLK / DVP0CLK P3 O TV Encoder 0 Clock Out. Output to TV encoder. Internally

pulled

down.

The above pins may be connected to an external TV Encoder chip such as a VIA VT1622A or

VT1622AM for driving a TV set.

I/O pads for the pins on this page are powered by VCCGFX (3.3V I/O).

AGP-Multiplexed Digital Video Port 1 (GDVP1) – TMDS Interface

Signal Name AGP Name Pin # I/O Signal Description

GDVP1D11

GDVP1D10

GDVP1D9

GDVP1D8

GDVP1D7

GDVP1D6

GDVP1D5

GDVP1D4

GDVP1D3

GDVP1D2

GDVP1D1

GDVP1D0

GC#BE3

GD26

GD24

GD30

GD28

GD29

GSBA4#

GD27

GSBA5#

GSBSTBS

GSBSTBF

GSBA2#

AC7

AE6

AF6

AE4

AF5

AF4

AF2

AD5

AD3

AE1

AF1

AD1

O

Data.

GDVP1HS

GSBA3# AD2 O

Horizontal Sync.

GDVP1VS

GSBA0# AC2 O

Vertical Sync.

GDVP1DE

GSBA1# AC3 O

Data Enable.

GDVP1DET

GD31 AD4 I Display Detect. If VGA register 3C5.3E[0] = 1,

3C5.1A[4] will read 1 if a display is connected.

Tie to GND if not used.

GDVP1CLK

GSBA6# AE3 O

Clock.

GDVP1CLK#

GSBA7# AF3 O

Clock Complement.

The GDVP1 Digital Video Port is supported through multiplexing its interface signal pins with AGP

pins. GDVP1 can be configured as either a TMDS transmitter interface port or a TV Encoder interface

port. (see the TMDS Transmitter Interface and TV Encoder Interface pin lists below for details).

Analog Power / Ground

Signal Name Pin # I/O Signal Description

VCCATX

C22 P

Analog Power for HT Transmit.

3.3V ±5%. Connect

through a ferrite bead for isolation of digital switching noise.

GNDATX

C21 P

Analog Ground for HT Transmit.

Connect to main ground

plane through a ferrite bead for isolation of digital switching

noise.

VCCARX

E25 P

Analog Power for HT Receive.

3.3V ±5%. Connect through

a ferrite bead for isolation of digital switching noise.

GNDARX

E26 P

Analog Ground for HT Receive.

Connect to main ground

plane through a ferrite bead for isolation of digital switching

noise.

Reference Voltages

Signal Name Pin # I/O Signal Description

VLVREF

AF21 P V-Link Voltage Reference. 0.625V ±2% derived using a

resistive voltage divider (3K §Ù to

2.5V and 1K §Ù to ground). See Design Guide for details.

AGPVREF[1:0]

AC6,

AC13

P AGP Voltage Reference. 0.5 VCCQQ (0.75V) for AGP 2.0

(4x transfer mode) and 0.23 VCCQQ (0.35V) for AGP 3.0 (8x

transfer mode). See the Design Guide for additional

information and circuit implementation details..

5.2 VIA K8N800 North Bridge(4)

MiTac Secret

Confidential Document