8399

8399

N/B Maintenance

N/B Maintenance

79

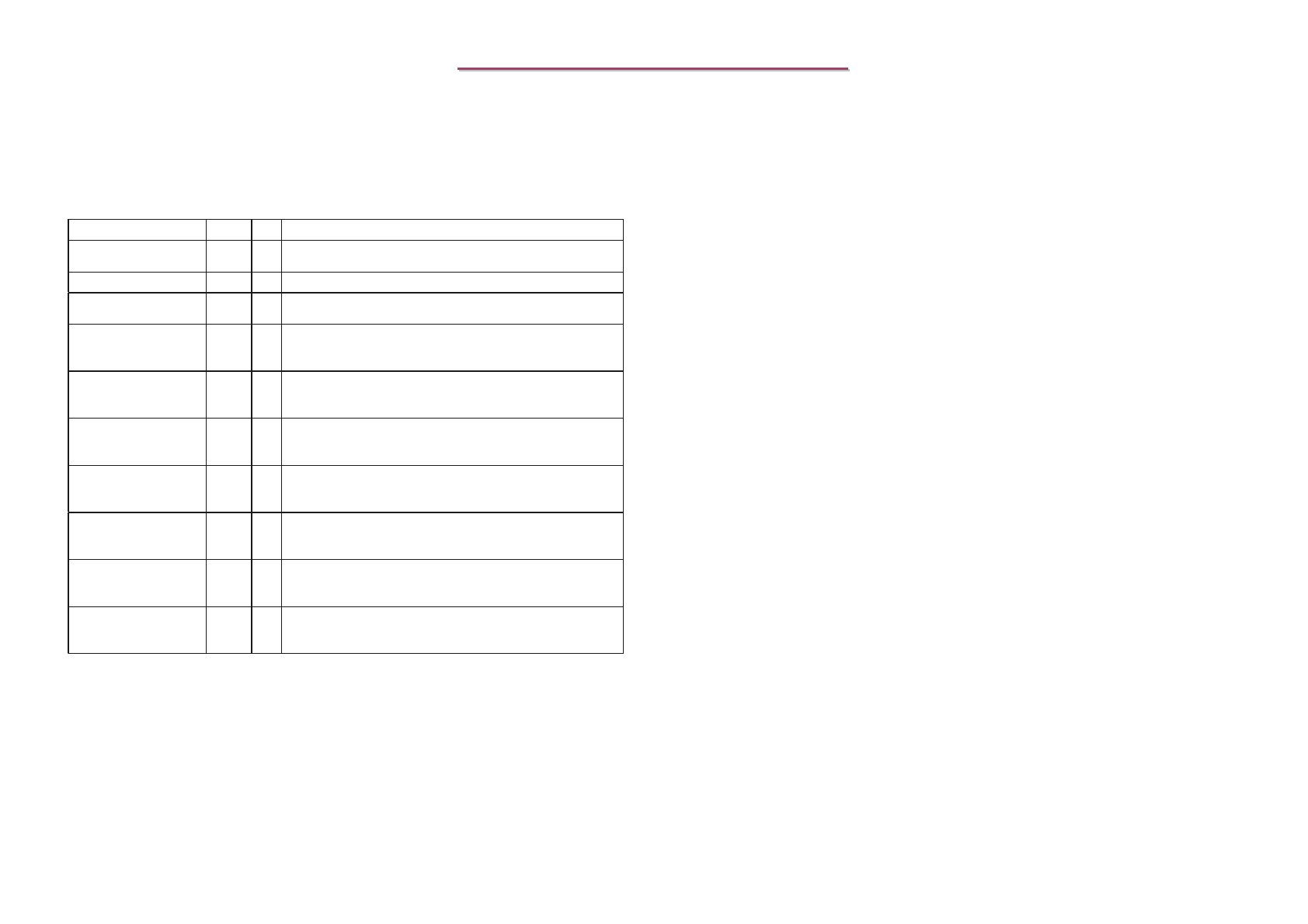

Integrated Graphics Power and Ground

Signal Name Pin # I/O Signal Description

VCCDAC

B2 P DAC Voltage. 3.3V ±5% connected via ferrite bead for

isolation of digital switching noise.

GNDDAC

C3, D4 P DAC Ground. Connect to main ground plane.

VCCRGB

A4 P Power for CRT RGB Outputs. 3.3V ±5% connected via

ferrite bead for isolation of digital switching noise

GNDRGB

B4 P

Connection point for RGB Load Resistors.

Connect to main

ground plane via ferrite bead for isolation of digital switching

noise.

VCCPLL1

D5 P Power for Graphics Controller PLL1 (“E-Clock”). 1.5V

±5% connected via ferrite bead for isolation of digital

switching noise.

GNDPLL1

C5 P

Ground for Graphics Controller PLL1 (“E-Clock”).

Connect to main ground plane via ferrite bead for isolation of

digital switching noise.

VCCPLL2

A5 P Power for Graphics Controller PLL2 (“D-Clock”). 1.5V

±5% connected via ferrite bead for isolation of digital

switching noise.

GNDPLL2

B5 P

Ground for Graphics Controller PLL2 (“D-Clock”).

Connect to main ground plane via ferrite bead for isolation of

digital switching noise.

VCCPLL3

A6 P Power for Graphics Controller PLL3 (“LCD Clock”). 1.5V

±5% connected via ferrite bead for isolation of digital

switching noise.

GNDPLL3

B6 P

Ground for Graphics Controller PLL3 (“LCD Clock”).

Connect to main ground plane via ferrite bead for isolation of

digital switching noise.

5.2 VIA K8N800 North Bridge(7)

MiTac Secret

Confidential Document