8399

8399

N/B Maintenance

N/B Maintenance

81

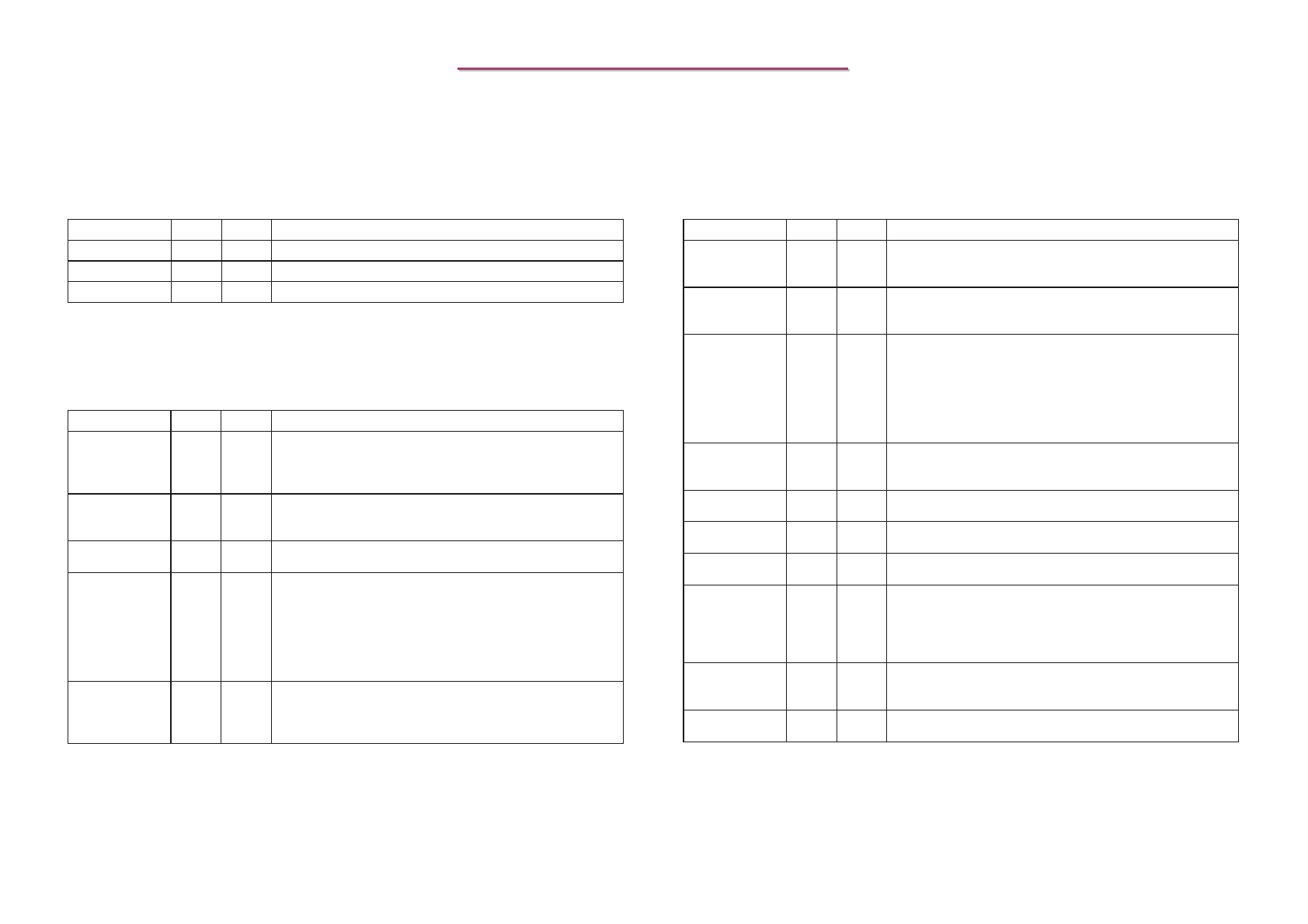

Advanced Programmable Interrupt Controller (APIC) Interface

Signal Name Pin # I/O Signal Description

APICD1

T23 O

Internal APIC Data 1.

Function 0 Rx58[6] = 1

APICD0 R25 O Internal APIC Data 0. Function 0 Rx58[6] = 1

APICCLK

U23 I

APIC Clock.

CPU Speed Control Interface

Signal Name Pin # I/O Signal Description

VRDSLP /

GPI29/ GPO29

AB9 OD Voltage Regulator Deep Sleep. Connected to the CPU voltage

regulator. High selectsthe proper voltage for deep sleep mode.

This pin performs the VRDPSLP function if

Function 0 RxE5[3] = 0.

GHI# / GPI22/

GPO22

R22 OD CPU Speed Select. Connected to the CPU voltage regulator,

used to select high speed (L) or low speed (H). This pin

performs the GHI# function if Function 0 RxE5[3] = 0.

DPSLP# /

GPI23/ GPO23

P21 OD CPU Deep Sleep. This pin performs the DPSLP# function if

Device 17 Function 0RxE5[3]=0.

CPUMISS /

GPI17

Y1 I CPU Missing. Used to detect the physical presence of the CPU

chip in its socket. High

indicates no CPU present. Connect to the CPUMISS pin of the

CPU socket. The state of

this pin may be read in the SMBus 2 registers. This pin may be

used as CPUMISS and

GPI17 at the same time.

AGPBZ# / GPI6 AD10 I AGP Busy. Low indicates that an AGP master cycle is in

progress (CPU speed transitions

will be postponed if this input is asserted low). Connected to the

AGP Bus AGPBZ# pin.

PCI Bus Interface

Signal Name Pin # I/O Signal Description

AD[31:0]

(see

pinlist)

IO Address / Data Bus. Multiplexed address and data. The address

is driven with FRAME#assertion and data is driven or received

in following cycles.

CBE[3:0]# M3, L4,

C1, E2

IO Command / Byte Enable. The command is driven with

FRAME# assertion. Byteenables corresponding to supplied or

requested data are driven on following clocks.

DEVSEL#

H2 IO

Device Select.

The VT8235 Version CE asserts this signal to

claim PCI transactions

through positive or subtractive decoding. As an input,

DEVSEL# indicates the response

to a VT8235 Version CE-initiated transaction and is also

sampled when decoding whether

to subtractively decode the cycle.

FRAME#

J1 IO Frame. Assertion indicates the address phase of a PCI transfer.

Negation indicates that

one more data transfer is desired by the cycle initiator.

IRDY#

J2 IO Initiator Ready. Asserted when the initiator is ready for data

transfer.

TRDY#

H1 IO Target Ready. Asserted when the target is ready for data

transfer.

STOP#

K4 IO Stop. Asserted by the target to request the master to stop the

current transaction.

SERR#

C2 I System Error. SERR# can be pulsed active by any PCI device

that detects a system error

condition. Upon sampling SERR# active, the VT8235 Version

CE can be programmed to

generate an NMI to the CPU.

PERR#

C3 _ Parity Error. PERR#, sustained tri-state, is only for the

reporting of data parity errors

during all PCI transactions except for a Special Cycle.

PAR

F4 IO Parity. A single parity bit is provided over AD[31:0] and

C/BE[3:0]#.

5.3 VIA VT8235CD South Bridge(2)

MiTac Secret

Confidential Document