8399

8399

N/B Maintenance

N/B Maintenance

83

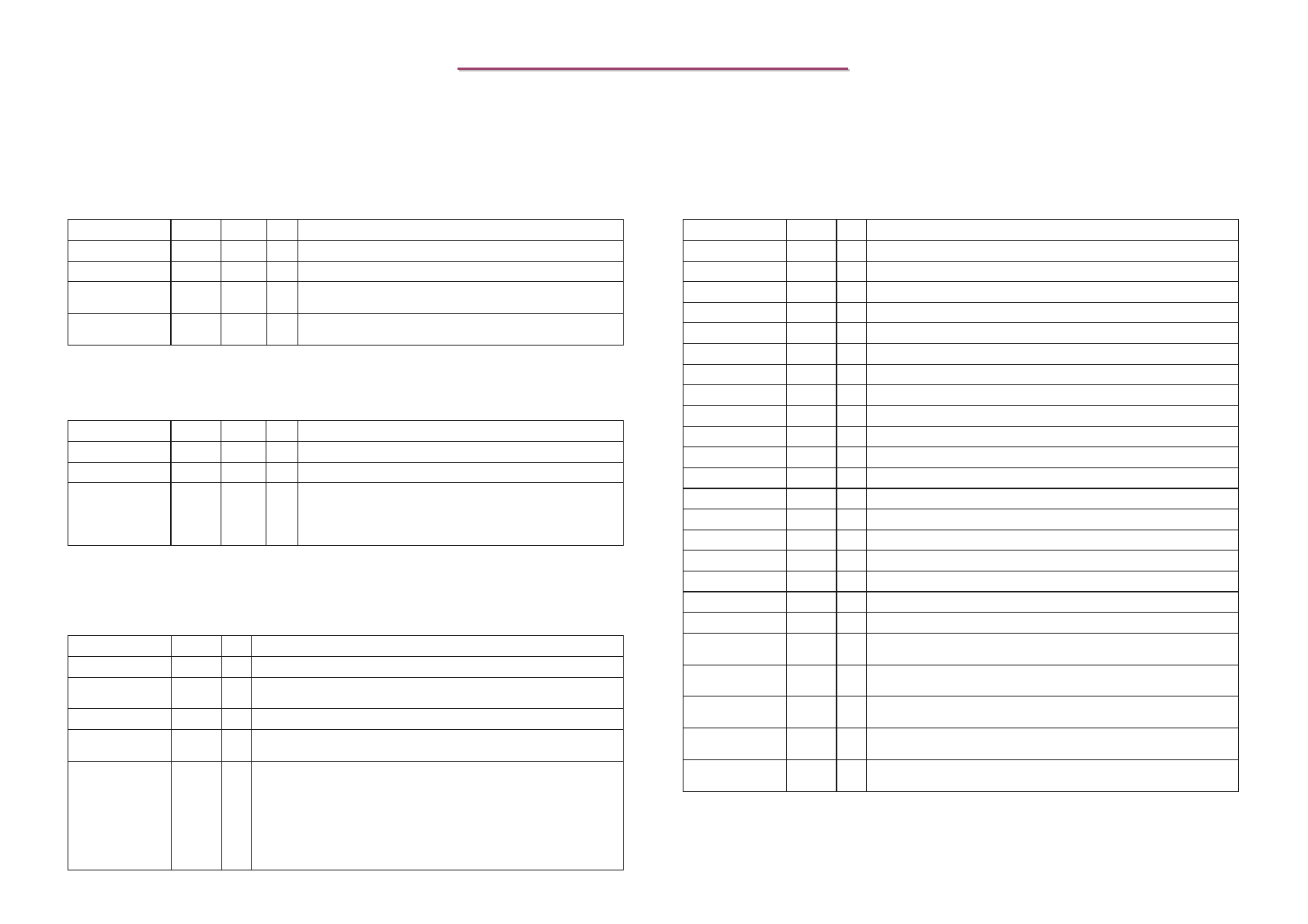

Serial EEPROM Interface

Signal Name Pin # I/O PU Signal Description

EECS# D11 O

Serial EEPROM Chip Select.

EECK C12 O

Serial EEPROM Clock.

EEDO B12 I

Serial EEPROM Data Output. Connect to EEPROM Data

Out pin.

EEDI A12 O

Serial EEPROM Data Input.

Connect to EEPROM Data

In pin.

Low Pin Count (LPC) Interface

Signal Name Pin # I/O PU Signal Description

LFRM# AF6 IO

LPC Frame.

LREQ# AE6 IO

LPC DMA / Bus Master Request.

LAD[3-0] AD7,

AE7,

AF7,

AD8

IO PU

LPC Address / Data.

Note: Connect the LPC interface LPCRST# (LPC Reset) signal to PCIRST#

Universal Serial Bus 2.0 Interface

Signal Name Pin # I/O Signal Description

USBP0+

E20 IO

USB 2.0 Port 0 Data +

USBP0ΠD20 IO

USB 2.0 Port 0 Data Œ

USBP1+ A20 IO

USB 2.0 Port 1 Data +

USBP1ΠB20 IO

USB 2.0 Port 1 Data Œ

USBP2+ E18 IO

USB 2.0 Port 2 Data +

USBP2ΠD18 IO

USB 2.0 Port 2 Data Œ

USBP3+ A18 IO

USB 2.0 Port 3 Data +

USBP3ΠB18 IO

USB 2.0 Port 3 Data Œ

USBP4+ D16 IO

USB 2.0 Port 4 Data +

USBP4ΠE16 IO

USB 2.0 Port 4 Data Œ

USBP5+ A16 IO

USB 2.0 Port 5 Data +

USBP5ΠB16 IO

USB 2.0 Port 5 Data Œ

USBCLK E23 I USB 2.0 Clock. 48MHz clock input for the USB interface

USBOC0# C26 I USB 2.0 Port 0 Over Current Detect. Port 0 is disabled if low.

USBOC1# D24 I USB 2.0 Port 1 Over Current Detect. Port 1 is disabled if low.

USBOC2# B26 I USB 2.0 Port 2 Over Current Detect. Port 2 is disabled if low.

USBOC3# C25 I USB 2.0 Port 3 Over Current Detect. Port 3 is disabled if low.

USBOC4# B24 I USB 2.0 Port 4 Over Current Detect. Port 4 is disabled if low.

USBOC5# A24 I USB 2.0 Port 5 Over Current Detect. Port 5 is disabled if low.

USBVCC (see pin

list)

Pow

er

USB 2.0 Port Differential Output Interface Logic Voltage.

3.3V

USBGND (see pin

list)

Pow

er

USB 2.0 Port Differential Output Interface Logic Ground.

VSUSUSB C24

Pow

er

USB 2.0 Suspend Power. 2.5V ±5%.

VCCUPLL A23,

B23

Pow

er

USB 2.0 PLL Analog Voltage. 2.5V ±5%.

GNDUPLL C23,

D23

Pow

er

USB 2.0 PLL Analog Ground.

System Management Bus (SMB) Interface (I 2 C Bus)

Signal Name

Pin #

I/O

Signal Description

SMBCK1

AC4 IO

SMB / I 2 C Channel 1 Clock.

SMBCK2 /

GPI27 / GPO27

AC3 IO SMB / I 2 C Channel 2 Clock. Rx95[2] = 0

SMBDT1

AB2 IO

SMB / I 2 C Channel 1 Data.

SMBDT2 /

GPI26 / GPO26

AD1 IO SMB / I 2 C Channel 2 Data. Rx95[2] = 0

SMBALRT#

AB1 I SMB Alert. (enabled by System Management Bus I/O space

Rx08[3] =

1) When the chip is enabled to allow it, assertion generates an IRQ

or

SMI interrupt or a power management resume event. Connect to a

10K

ohm pullup to VSUS33 if not used.

5.3 VIA VT8235CD South Bridge(4)

MiTac Secret

Confidential Document