8399

8399

N/B Maintenance

N/B Maintenance

78

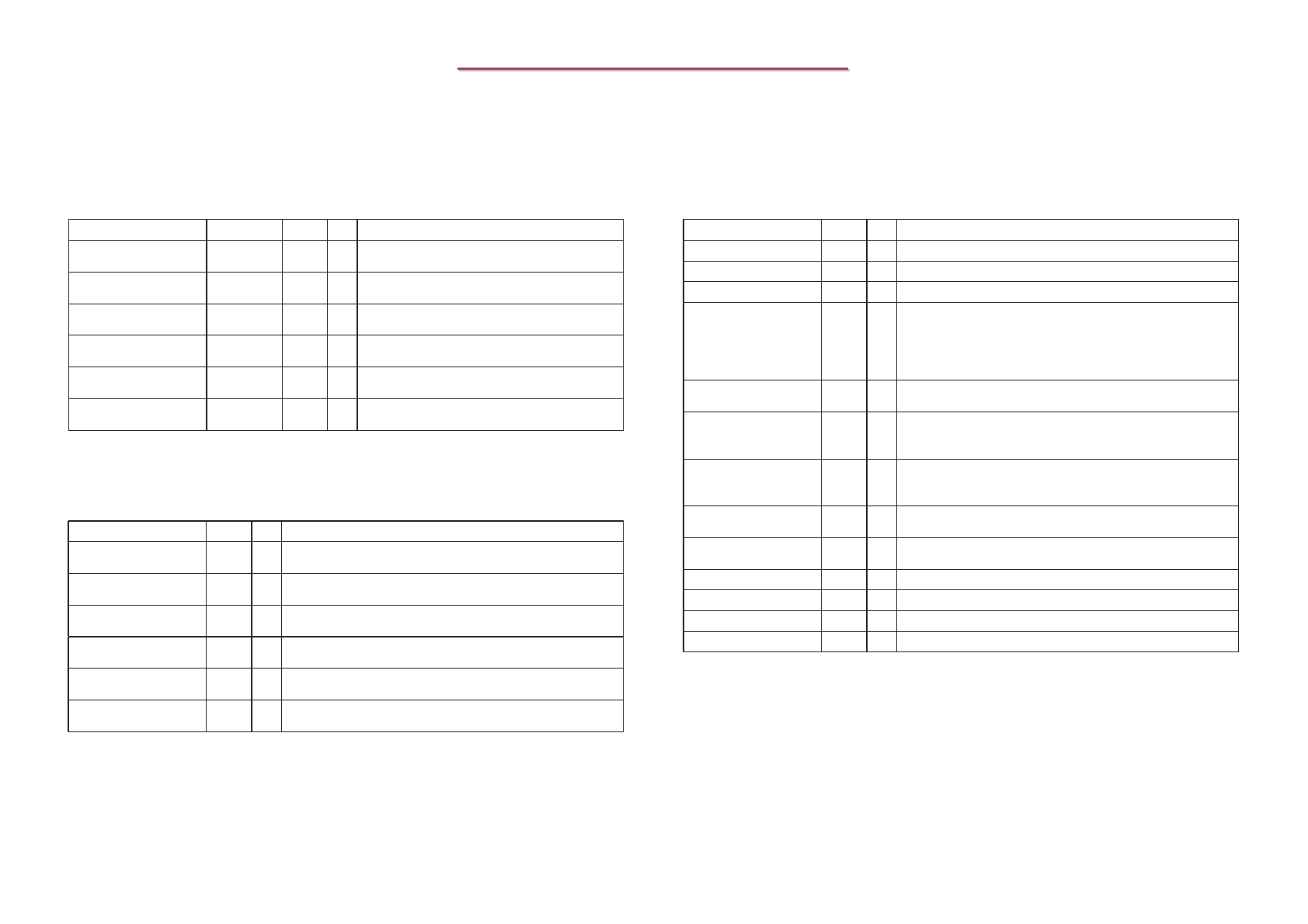

24-Bit / Dual 12-Bit Flat Panel Display Interface (Continued)

Signal Name AGP Name Pin # I/O Signal Description

FP1HS

GD9 AD14 O Flat Panel Horizontal Sync. For port 1 in dual

12-bit mode.

FP1VS

GPAR AC16 O

Flat Panel Vertical Sync.

For port 1 in dual

12-bit mode.

FP1DE

GSERR AC15 O Flat Panel Data Enable. For port 1 in dual

12-bit mode.

FP1DET

GD8 AF14 I Flat Panel Detect. For port 1 in dual 12-bit

mode.

FP1CLK

GD2 AE18 O Flat Panel Clock. For port 1 in dual 12-bit

mode.

FP1CLK#

GSTOP AC12 O Flat Panel Clock Complement. For port 1 in

dual 12-bit mode.

Clock, Reset, Power Control, General Purpose I/O, Interrupts and Test

Signal Name Pin # I/O Signal Description

GCLK

A11 I AGP Clock. 66 MHz clock for AGP logic.

DCLKI

D7 I Dot Clock (Pixel Clock) In. For spread spectrum.

DCLKO

A7 O Dot Clock (Pixel Clock) Out. For spread spectrum.

RESET#

AD25 I Reset. Input from the South Bridge chip. 3.3V tolerant input.

When asserted, this signal resets the chip and sets all register

bits to the default value. The rising edge of this signal is used

to sample all power-up strap options In addition, HTRST# is

driven active to reset the K8 CPU.

PWROK

AE26 I Power OK. Driven by South Bridge PWROK output from the

power supply PWRGOOD input to the South Bridge.

SUSST#

AD26 I Suspend Status. For implementation of the

Suspend-to-DRAM feature. Connect to an external pull-up to

disable.

TESTIN

AC26 I Test In. This pin is used for testing and must be left

unconnected or tied high (4.7K §Ù to 2.5V) on all board

designs.

BISTIN

D3 I Built-In-Self-Test In. Reserved for test. Connect to GND for

normal operation.

DEBUG

AC17 I

Debug.

Reserved for test. Connect to ground for normal

operation.

XIN

C6 I Reference Frequency In. 14.31818 MHz.

INTA#

E7 O PCI Interrupt Output A. Connect to the South Bridge.

GPOUT

D2 O

General Purpose Output.

GPO0

N2 O

General Purpose Output.

Compensation

Signal Name Pin # I/O Signal Description

RPCOMP

D25 AI Host CPU P-Channel Compensation. Connect 50 §Ù 1%

resistor to GND.

RNCOMP

D26 AI Host CPU N-Channel Compensation. Connect 50 §Ù 1%

resistor to VCCHT.

RTCOMP

C26 AI Host CPU Compensation. Connect 100 §Ù 1% resistor to

VCCHT.

VLPCOMP

AD19 AI V-Link P-Channel Compensation. Connect 360 §Ù 1%

resistor to ground.

AGPNCOMP

W1 AI AGP N-Channel Compensation. Connect 60.4 §Ù 1%

resistor to VCCAGP.

AGPPCOMP

V1 AI AGP P-Channel Compensation. Connect 60.4 §Ù 1%

resistor to GND.

5.2 VIA K8N800 North Bridge(6)

MiTac Secret

Confidential Document