Chapter 5 Signal Timing

© National Instruments Corporation 5-27 DIO 6533 User Manual

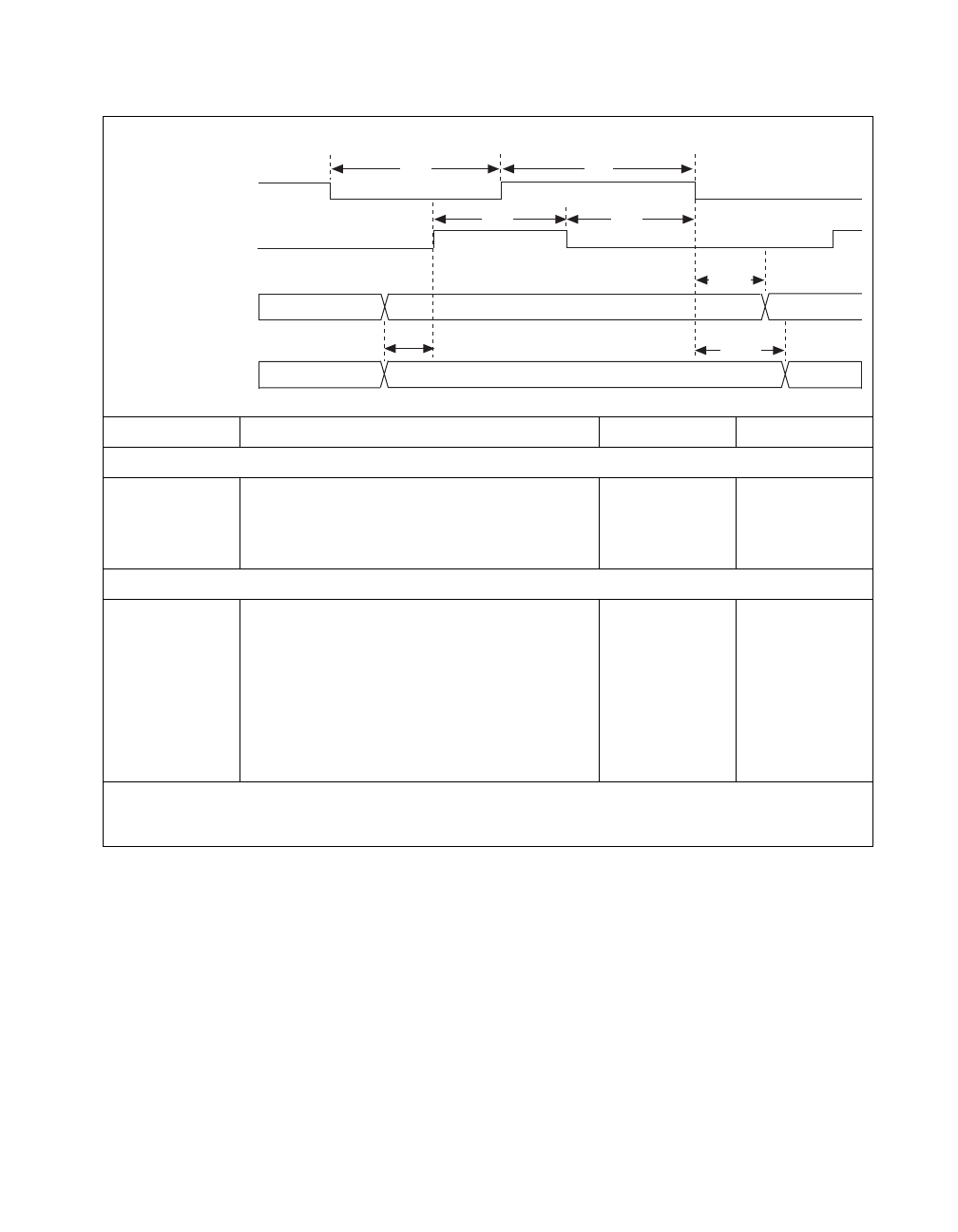

Figure 5-23. Trailing-Edge Mode Output Timing

Burst Mode

Burst mode is a synchronous, or clocked, protocol. The data transmitter

and receiver share a clock signal over the PCLK line.

In every clock cycle, the 6533 device asserts the ACK signal if it is

ready to perform a transfer. If the peripheral device also asserts the REQ

signal, a transfer occurs on the rising clock edge. Either the 6533 device

or the peripheral device can insert wait states into the protocol by

Parameter Description Minimum Maximum

Input Parameters

t

rr*

REQ pulse width

75 —

t

r*r

REQ inactive duration

75 —

t

a*r*

ACK inactive to next REQ inactive

0—

Output Parameters

t

aa*

ACK pulse width

225

1

275

2

t

r*do(1)

REQ inactive to new output data

(with REQ-edge latching)

050

t

r*do(2)

REQ inactive to new output data

(with REQ-edge latching disabled)

0—

t

doa

Output data valid to ACK

(with REQ-edge latching disabled)

25 —

1

t

aa*

(min)

= 225 + programmable delay All timing values are in nanoseconds.

2

t

aa*

(max) = 275 + programmable delay

REQ

ACK

Output Data

(REQ-edge latching)

Output Data

(REQ-edge

latching disabled)

t

r*r

t

r*do(1)

t

doa

t

aa*

t

a*r*

t

rr*

t

r*do(2)