Chapter 5 Signal Timing

DIO 6533 User Manual 5-32 © National Instruments Corporation

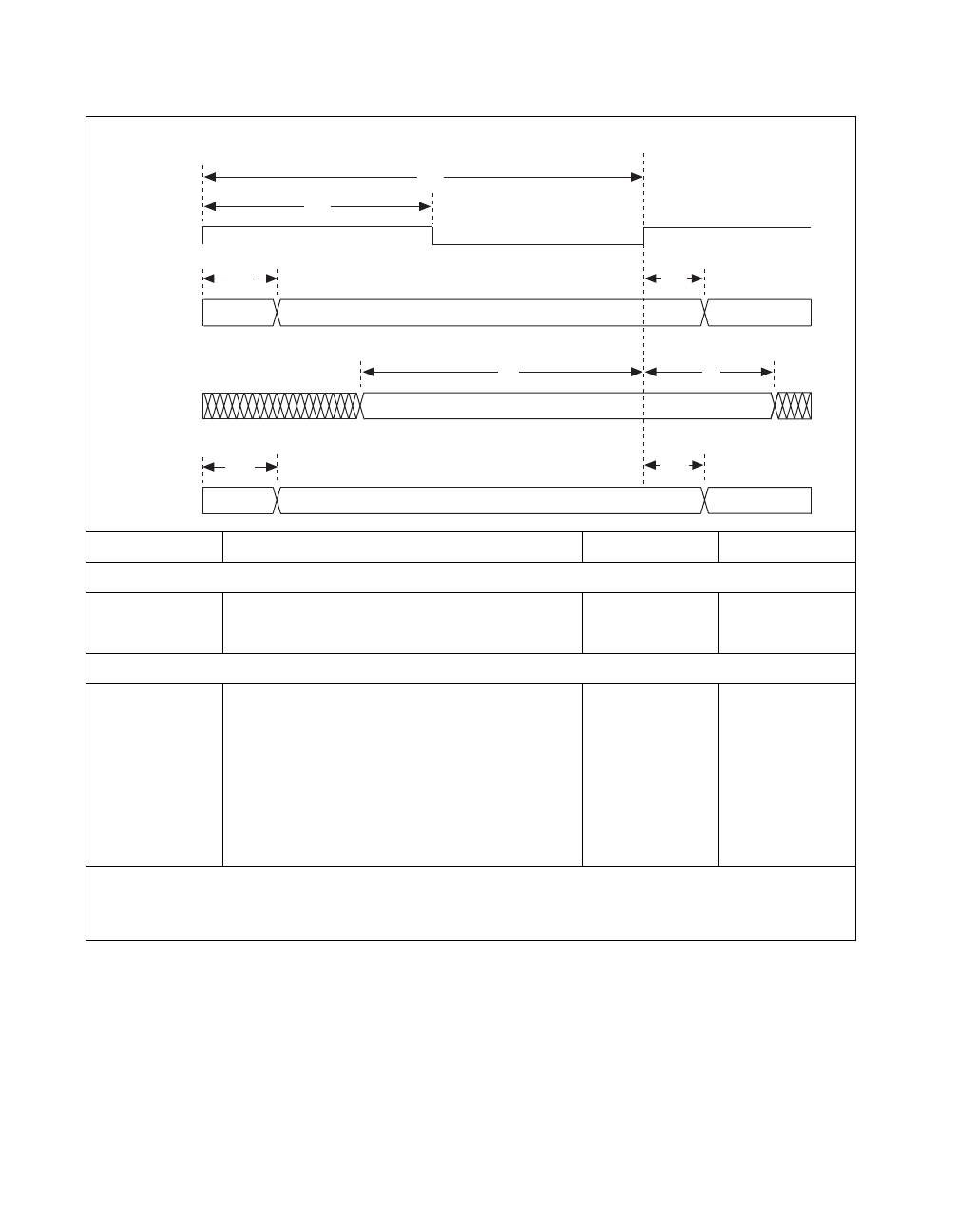

Figure 5-28. Burst Mode Output Timing (PCLK Reversed)

Parameter Description Minimum Maximum

Input Parameters

t

rs

Setup time from REQ valid to PCLK

12 —

t

rh

Hold time from PCLK to REQ invalid

0—

Output Parameters

t

pc

PCLK cycle time

50 700

1

t

pw

PCLK high pulse duration

t

pc

/2 - 5 t

pc

/2 + 5

t

pa

PCLK to ACK valid

—18

t

ah

Hold time from PCLK to ACK invalid

3—

t

pdo

PCLK to output data valid

—28

t

doh

Hold time from PCLK to output data invalid

4—

1

t

pc

= programmable delay from 100 to 700 ns, or 50 ns if programmable delay is 0. Timebase

stability for the board 20 MHz clock source is 50 ppm.

All timing values are in nanoseconds.

PCLK

ACK

Data Out

REQ

t

rs

t

pa

t

pdo

t

pw

t

pc

t

doh

t

rh

t

ah