Rev.2.00 Nov 28, 2005 page 107 of 378

REJ09B0124-0200

M16C/6N Group (M16C/6NK, M16C/6NM) 12. DMAC

Under development

This document is under development and its contents are subject to change.

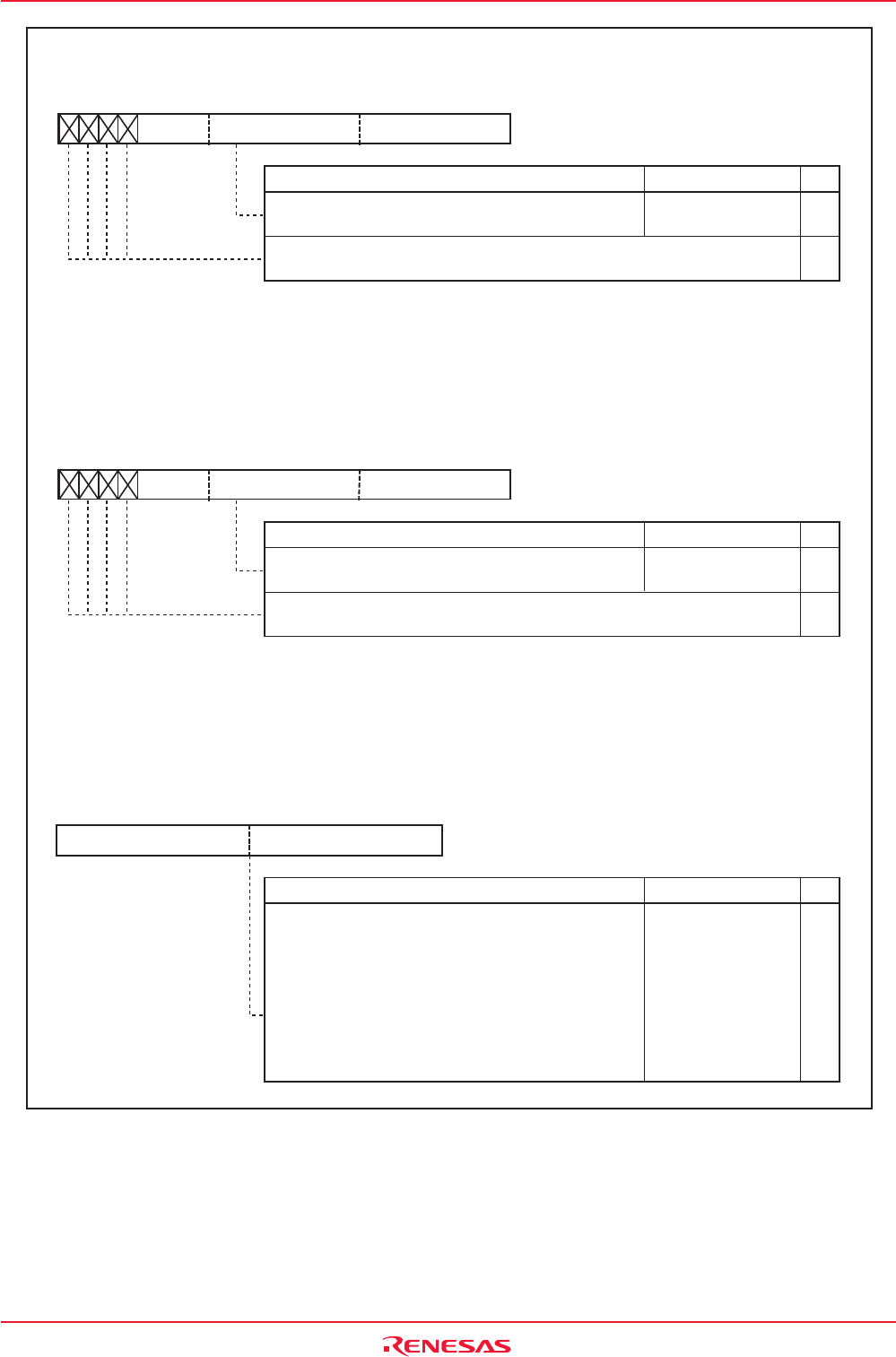

Figure 12.4 SAR0 and SAR1 Registers, DAR0 and DAR1 Registers, TCR0 and TCR1 Registers

Symbol After Reset

SAR0

SAR1

Indeterminate

Indeterminate

Setting Range

RW

RW

-

00000h to FFFFFh

b0 b7 b0b3

(b19) (b16)

b7 b0

(b15) (b8)

b7

(b23)

DMAi Source Pointer (i = 0, 1)

(1)

Nothing is assigned. When write, set to "0".

When read, their contents are "0".

Set the source address of transfer

Function

Address

0022h to 0020h

0032h to 0030h

NOTE:

1. If the DSD bit in the DMiCON register is "0" (fixed), this register can only be written to when the DMAE bit in the

DMiCON register is "0" (DMA disabled).

If the DSD bit is "1" (forward direction), this register can be written to at any time.

If the DSD bit is "1" and the DMAE bit is "1" (DMA enabled), the DMAi forward address pointer can be read from

this register. Otherwise, the value written to it can be read.

Set the transfer count minus 1.

The written value is stored in the DMAi transfer counter

reload register, and when the DMAE bit in the DMiCON

register is set to "1" (DMA enabled) or the DMAi transfer

counter underflows when the DMASL bit in the DMiCON

register is "1" (repeat transfer), the value of the DMAi

transfer counter reload register is transferred to the DMAi

transfer counter.

When read, the DMAi transfer counter is read.

Function

Address

0029h, 0028h

0039h, 0038h

DMAi Transfer Counter (i = 0, 1)

Symbol After Reset

TCR0

TCR1

Indeterminate

Indeterminate

b0 b7

(b8)

b0b7

(b15)

Setting Range

RW

RW

0000h to FFFFh

Symbol After Reset

DAR0

DAR1

Indeterminate

Indeterminate

Setting Range

RW

RW

-

00000h to FFFFFh

b0 b7 b0b3

(b19) (b16)

b7 b0

(b15) (b8)

b7

(b23)

DMAi Destination Pointer (i = 0, 1)

(1)

Function

Set the destination address of transfer

Nothing is assigned. When write, set to "0".

When read, their contents are "0".

Address

0026h to 0024h

0036h to 0034h

NOTE:

1. If the DAD bit in the DMiCON register is "0" (fixed), this register can only be written to when the DMAE bit in the

DMiCON register is "0" (DMA disabled).

If the DAD bit is "1" (forward direction), this register can be written to at any time.

If the DAD bit is "1" and the DMAE bit is "1" (DMA enabled), the DMAi forward address pointer can be read from

this register. Otherwise, the value written to it can be read.