Rev.2.00 Nov 28, 2005 page 261 of 378

REJ09B0124-0200

M16C/6N Group (M16C/6NK, M16C/6NM) 21. Flash Memory Version

Under development

This document is under development and its contents are subject to change.

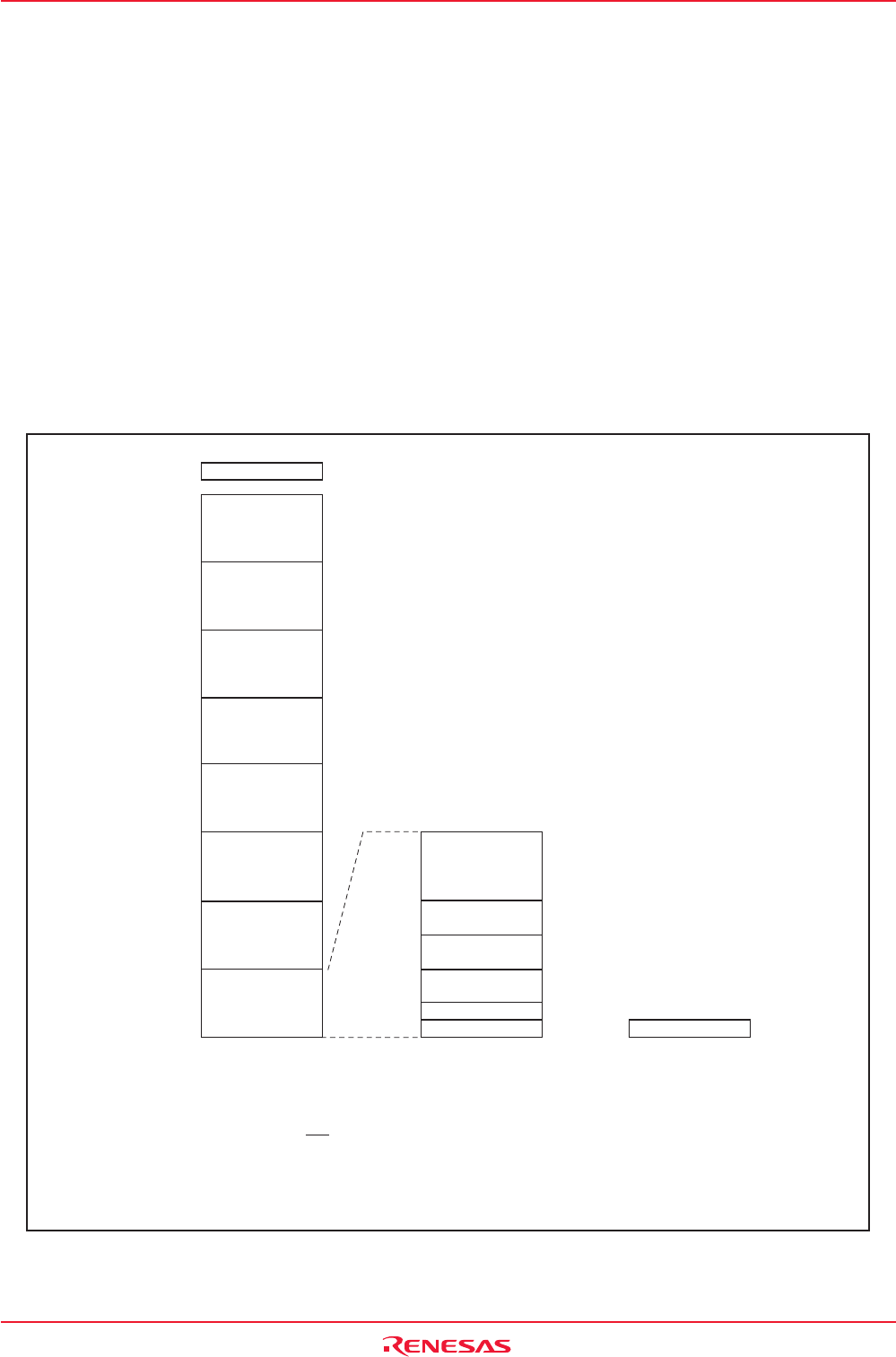

21.1 Memory Map

The flash memory contains the user ROM area and a boot ROM area. The user ROM area has space to

store the microcomputer operating program in single-chip mode or memory expansion mode and a separate

4-Kbyte space as the block A. (Not available memory expansion mode in T/V-ver..)

Figure 21.1 shows the block diagram of flash memory.

The user ROM area is divided into several blocks, each of which can individually be protected (locked)

against programming or erasure. The user ROM area can be rewritten in all of CPU rewrite, standard serial

I/O mode, parallel I/O mode and CAN I/O mode. Block A is enabled for use by setting the PM10 bit in the

_______

PM1 register to “1” (block A enabled. CS2 area at addresses 10000h to 26FFFh).

The boot ROM area is located at the same addresses as the user ROM area. It can only be rewritten in

parallel I/O mode (refer to 21.1.1 Boot Mode). A program in the boot ROM area is executed after a hardware

reset occurs while an “H ” signal is applied to the CNVSS and P5_0 pins and an “L” signal is applied to the

P5_5 pin (refer to 21.1.1 Boot Mode). A program in the user ROM area is executed after a hardware reset

occurs while an “L” signal is applied to the CNVSS pin. However, the boot ROM area cannot be read.

Figure 21.1 Flash Memory Block Diagram

Boot ROM area

(2)

4 Kbytes

0FF000h

0FFFFFh

Block 5: 32 Kbytes

Block 4: 8 Kbytes

Block 3: 8 Kbytes

Block 2: 8 Kbytes

Block 1: 4 Kbytes

Block 0: 4 Kbytes

0F0000h

0F7FFFh

0F8000h

0F9FFFh

0FA000h

0FBFFFh

0FC000h

0FDFFFh

0FE000h

0FEFFFh

0FF000h

0FFFFFh

Block 8: 64 Kbytes

Block 7: 64 Kbytes

Block 6: 64 Kbytes

Block 5 to 0

(32+8+8+8+4+4) Kbytes

User ROM area

Block 12: 64 Kbytes

Block 11: 64 Kbytes

Block 10: 64 Kbytes

Block 9: 64 Kbytes

080000h

08FFFFh

090000h

09FFFFh

0A0000h

0AFFFFh

0B0000h

0BFFFFh

0C0000h

0CFFFFh

0D0000h

0DFFFFh

0E0000h

0EFFFFh

0F0000h

0FFFFFh

Block A: 4 Kbytes

(1)

00F000h

00FFFFh

* Shown here is a block diagram during single-chip mode.

NOTES:

1. Block A can be made usable by setting the PM10 bit in the PM1 register to "1" (block A enabled, addresses

10000h to 26FFFh for CS2 area).

Block A cannot be erased by the erase all unlocked block command. Use the block erase command to

erase it.

2. The boot ROM area can only be rewritten in parallel I/O mode.

3. To specify a block, use an even address in that block.