Rev.2.00 Nov 28, 2005 page 157 of 378

REJ09B0124-0200

M16C/6N Group (M16C/6NK, M16C/6NM) 15. Serial Interface

Under development

This document is under development and its contents are subject to change.

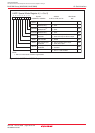

Figure 15.9 U0SMR2 to U2SMR2 Registers and U0SMR3 to U2SMR3 Registers

b7 b6 b5 b4 b3 b2 b1 b0

Function

UARTi Special Mode Register 2 (i = 0 to 2)

Bit Name

Bit

Symbol

Symbol Address After Reset

U0SMR2 to U2SMR2 01EEh, 01F2h, 01F6h X0000000b

RW

IICM2

CSC

SWC

Clock-Synchronous

Bit

SCL Wait Output Bit

I

2

C Mode Select Bit 2

ALS

SDA Output Stop Bit

See Table 15.12 I

2

C Mode Functions

0 : Disabled

1 : Enabled

0 : Disabled

1 : Enabled

0 : Disabled

1 : Enabled

RW

RW

RW

RW

Nothing is assigned. When write, set to "0".

When read, its content is indeterminate.

-

(b7)

-

SDA Output Disable

Bit

SDHI

0: Enabled

1: Disabled (high-impedance)

RW

SCL Wait Output

Bit 2

SWC2

0: Transfer clock

1: "L" output

RW

UARTi Initialization

Bit

STAC

0 : Disabled

1 : Enabled

RW

b7 b6 b5

NOTES:

1. The DL2 to DL0 bits are used to generate a delay in SDAi output by digital means during I

2

C mode.

In other than I

2

C mode, set these bits to "000b" (no delay).

2. The amount of delay varies with the load on SCLi and SDAi pins. Also, when using an external clock,

the amount of delay increases by about 100 ns.

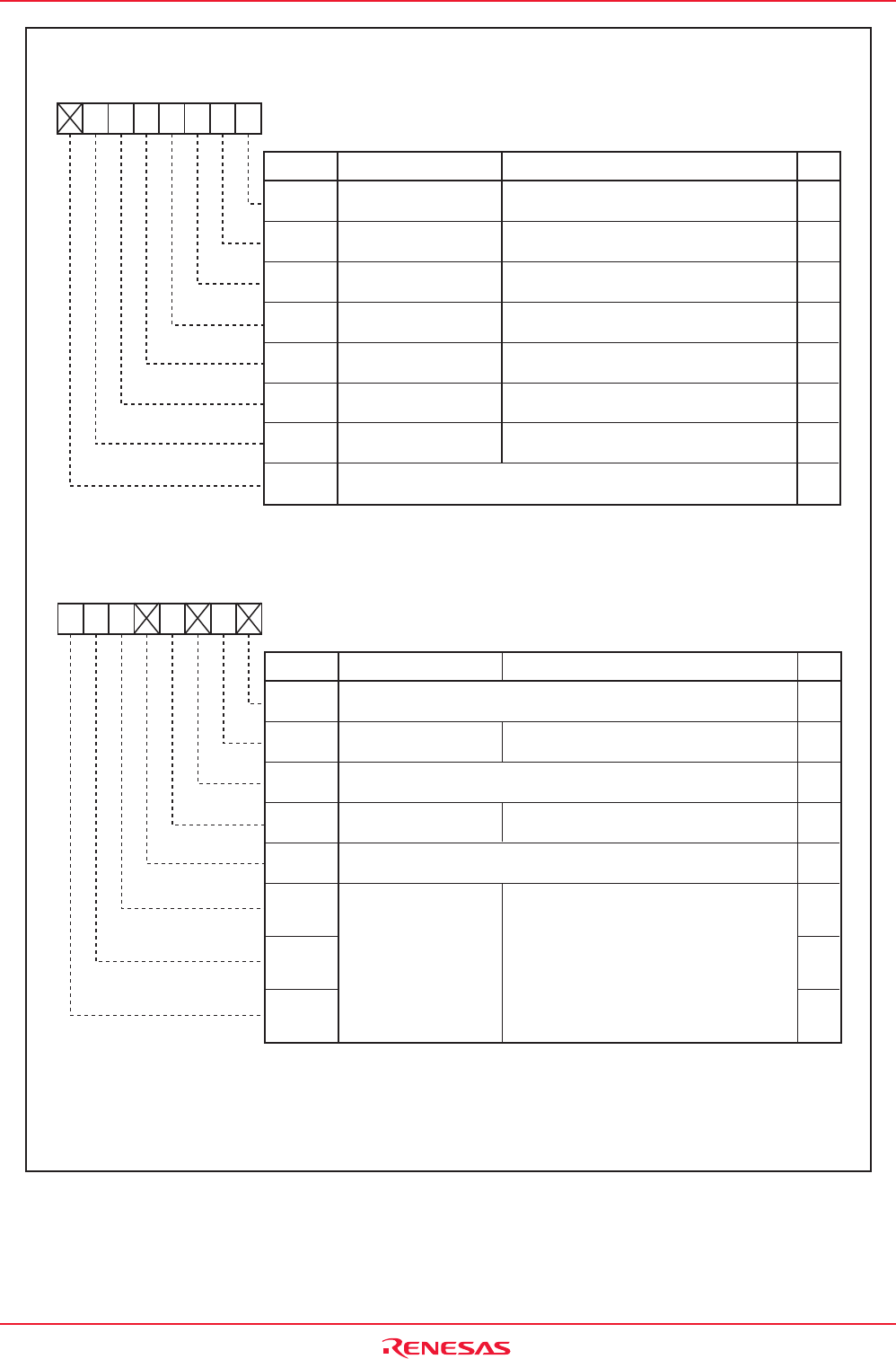

b7 b6 b5 b4 b3 b2 b1 b0

Function

UARTi Special Mode Register 3 (i = 0 to 2)

Bit Name

Bit

Symbol

Symbol Address After Reset

U0SMR3 to U2SMR3 01EDh, 01F1h, 01F5h 000X0X0Xb

RW

-

(b0)

CKPH

-

(b2)

Clock Phase Set Bit

Nothing is assigned. When write, set to "0".

When read, its content is indeterminate.

-

(b4)

Nothing is assigned. When write, set to "0".

When read, its content is indeterminate.

Nothing is assigned When write, set to "0".

When read, its content is indeterminate.

NODC

Clock Output Select

Bit

0 : Without clock delay

1 : With clock delay

0 : CLKi is CMOS output

1 : CLKi is N channel open-drain output

RW

-

-

RW

DL2

DL1 RW

RW

SDAi Digital Delay

Setup Bit

(1) (2)

DL0

0 0 0 : Without delay

0 0 1 :

1 to 2 cycle(s) of UiBRG count source

0 1 0 :

2 to 3 cycles of UiBRG count source

0 1 1 :

3 to 4 cycles of UiBRG count source

1 0 0 :

4 to 5 cycles of UiBRG count source

1 0 1 :

5 to 6 cycles of UiBRG count source

1 1 0 :

6 to 7 cycles of UiBRG count source

1 1 1 :

7 to 8 cycles of UiBRG count source

RW

-