Rev.2.00 Nov 28, 2005 page 275 of 378

REJ09B0124-0200

M16C/6N Group (M16C/6NK, M16C/6NM) 21. Flash Memory Version

Under development

This document is under development and its contents are subject to change.

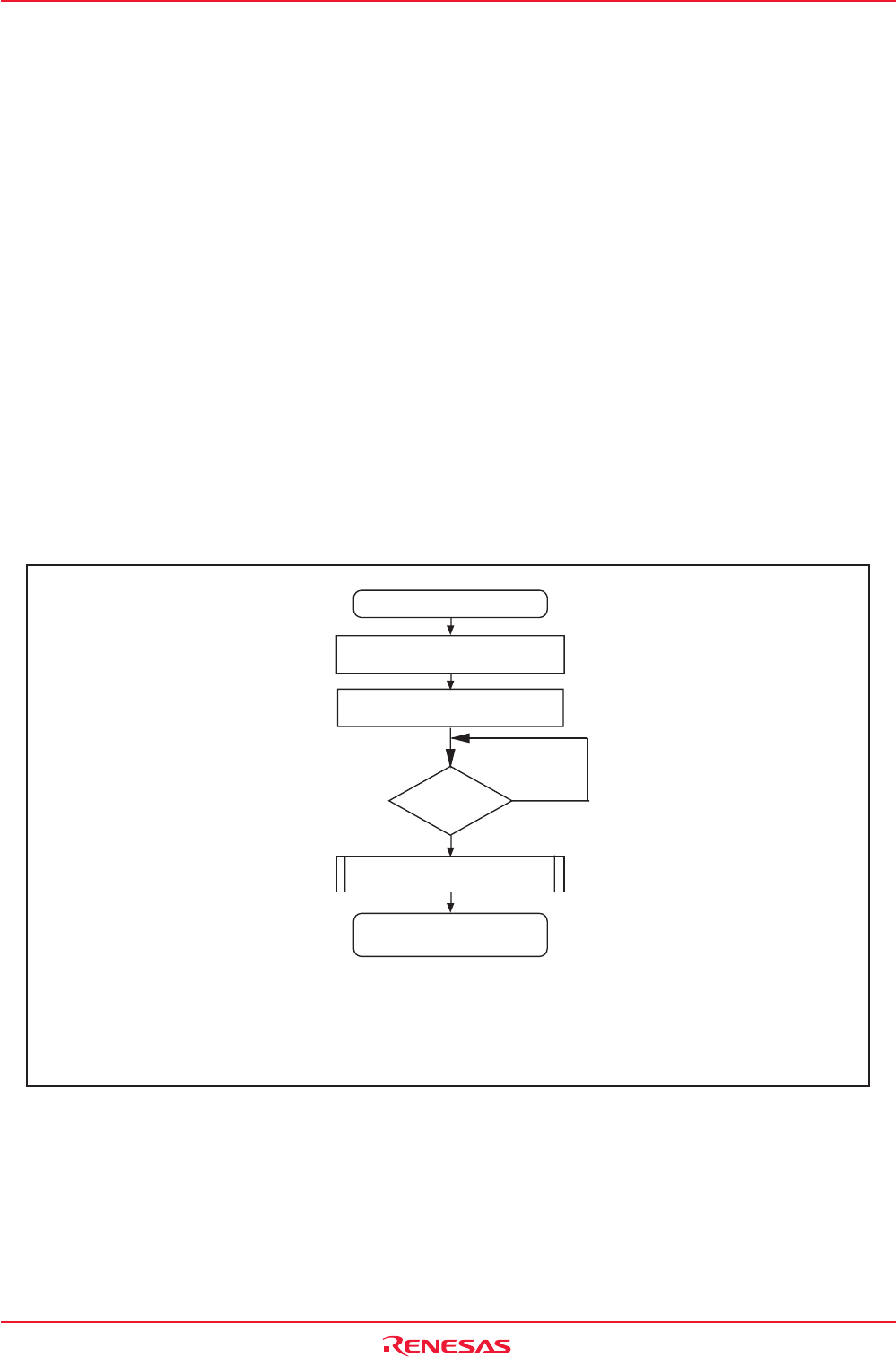

Figure 21.9 Block Erase Command

21.3.5.5 Block Erase Command

The block erase command erases each block.

By writing “xx20h” in the first bus cycle and “xxD0h” to the highest-order even address of a block in the

second bus cycle, an auto erase operation (erase and verify) will start in the specified block.

The FMR00 bit in the FMR0 register indicates whether an auto erase operation has been completed.

The FMR00 bit is set to “0” (busy) during auto erase and to “1” (ready) when the auto erase operation is

completed.

After the completion of an auto erase operation, the FMR07 bit in the FMR0 register indicates whether

or not the auto erase operation has been completed as expected. (Refer to 21.3.8 Full Status Check.)

Figure 21.9 shows a flow chart of the block erase command programming.

The lock bit protects each block from being programmed inadvertently. (Refer to 21.3.6 Data Protect

Function.)

In EW1 mode, do not execute this command on the block where the rewrite control program is allocated.

In EW0 mode, the microcomputer enters read status register mode as soon as an auto erase operation

starts. The status register can be read. The SR7 bit in the status register is set to “0” at the same time an

auto erase operation starts. It is set to “1” when an auto erase operation is completed. The microcomputer

remains in read status register mode until the read array command or read lock bit status command is

written. Also execute the clear status register command and block erase command at least 3 times until

an erase error is not generated when an erase error is generated.

Write "xxD0h" to the highest-order

block address

Start

YES

NO

FMR00=1?

Full status check

(2) (3)

Block erase operation is

completed

Write the command code "xx20h"

NOTES:

1.Write the command code and data to even addresses.

2.Refer to Figure 21.12 Full Status Check and Handling Procedure for Each Error.

3.Execute the clear status register command and block erase command at least 3 times

until an erase error is not generated when an erase error is generated.