Rev.2.00 Nov 28, 2005 page 37 of 378

REJ09B0124-0200

M16C/6N Group (M16C/6NK, M16C/6NM) 5. Reset

Under development

This document is under development and its contents are subject to change.

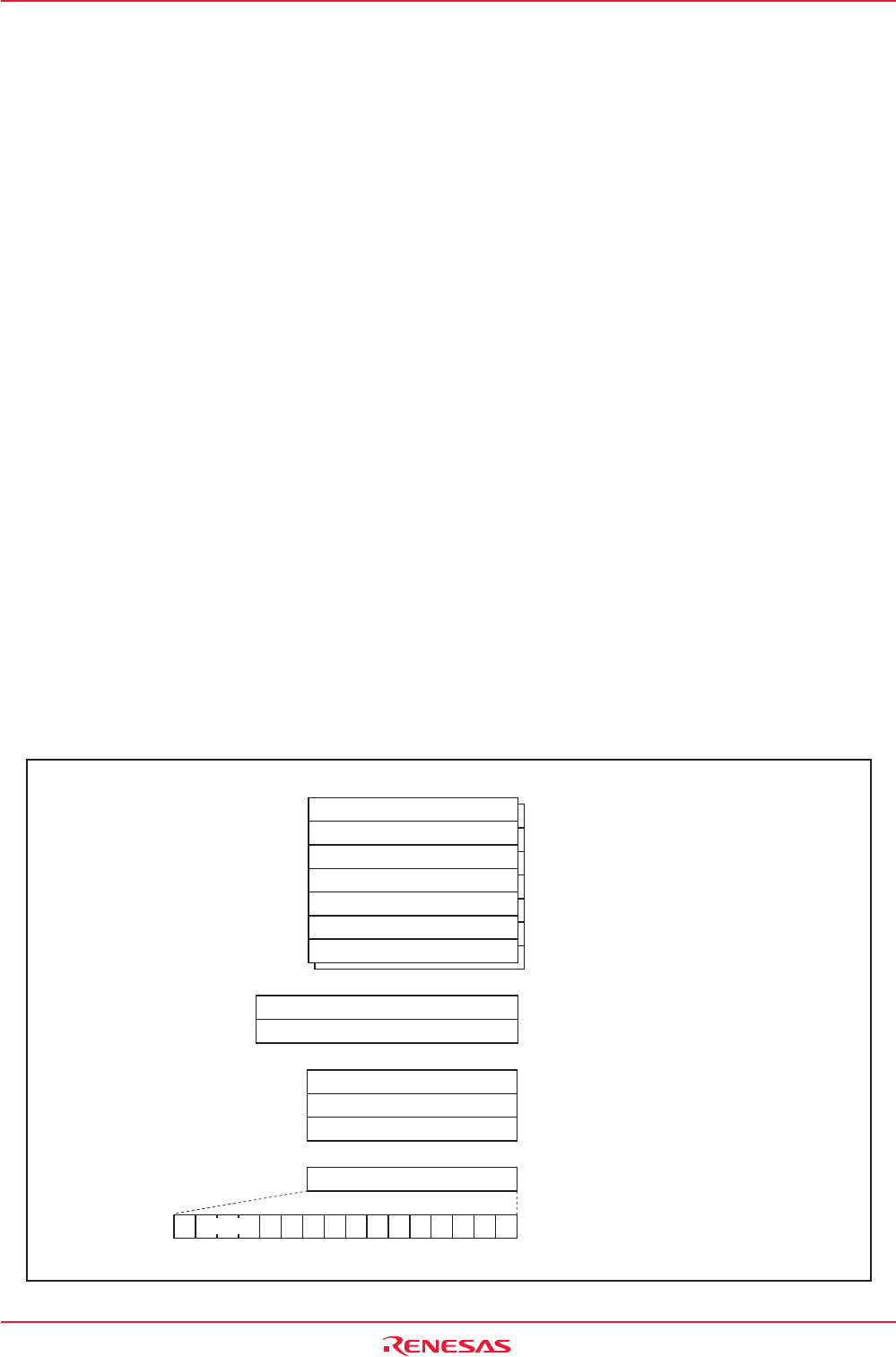

Figure 5.3 CPU Register Status After Reset

0000h

0000h

0000h

b15 b0

Static Base Register (SB)

User Stack Pointer (USP)

Interrupt Stack Pointer (ISP)

b19

00000h

b0

Interrupt Table Register (INTB)

Content of addresses FFFFEh to FFFFCh

Program Counter (PC)

b15 b0

0000h

0000h

0000h

0000h

0000h

0000h

0000h

Data Register (R0)

Data Register (R1)

Data Register (R2)

Data Register (R3)

Address Register (A0)

Address Register (A1)

Frame Base Register (FB)

b15 b0

b15 b0

0000h

Flag Register (FLG)

IPL U I O B S Z D C

b7b8

5.2 Software Reset

The microcomputer resets pins, the CPU and SFR when the PM03 bit in the PM0 register is set to “1”

(microcomputer reset). Then the microcomputer executes the program in an address determined by the reset vector.

Set the PM03 bit to “1” while the main clock is selected as the CPU clock and the main clock oscillation is stable.

In the software reset, the microcomputer does not reset a part of the SFR. Refer to 4. Special Function

Register (SFR) for details.

Processor mode remains unchanged since the PM01 to PM00 bits in the PM0 register are not reset.

5.3 Watchdog Timer Reset

The microcomputer resets pins, the CPU and SFR when the PM12 bit in the PM1 register is set to “1” (reset

when watchdog timer underflows) and the watchdog timer underflows. Then the microcomputer executes

the program in an address determined by the reset vector.

In the watchdog timer reset, the microcomputer does not reset a part of the SFR. Refer to 4. Special

Function Register (SFR) for details.

Processor mode remains unchanged since the PM01 to PM00 bits in the PM0 register are not reset.

5.4 Oscillation Stop Detection Reset

The microcomputer resets and stops pins, the CPU and SFR when the CM27 bit in the CM2 register is “0”

(reset at oscillation stop, re-oscillation detection), if it detects main clock oscillation circuit stop. Refer to 8.5

Oscillation Stop and Re-Oscillation Detection Function for details.

In the oscillation stop detection reset, the microcomputer does not reset a part of the SFR. Refer to 4. Special

Function Register (SFR) for details.

Processor mode remains unchanged since the PM01 to PM00 bits in the PM0 register are not reset.

5.5 Internal Space

Figure 5.3 shows CPU register status after reset. Refer to 4. Special Function Register (SFR) for SFR

states after reset.