Rev.2.00 Nov 28, 2005 page 163 of 378

REJ09B0124-0200

M16C/6N Group (M16C/6NK, M16C/6NM) 15. Serial Interface

Under development

This document is under development and its contents are subject to change.

15.1.1.1 Counter Measure for Communication Error Occurs

If a communication error occurs while transmitting or receiving in clock synchronous serial I/O mode,

follow the procedures below.

• Resetting the UiRB register (i = 0 to 2)

(1) Set the RE bit in the UiC1 register to “0” (reception disabled)

(2) Set the SMD2 to SMD0 bits in the UiMR register to “000b” (serial interface disabled)

(3) Set the SMD2 to SMD0 bits in the UiMR register to “001b” (clock synchronous serial I/O mode)

(4) Set the RE bit in the UiC1 register to “1” (reception enabled)

• Resetting the UiTB register (i = 0 to 2)

(1) Set the SMD2 to SMD0 bits in the UiMR register to “000b” (serial interface disabled)

(2) Set the SMD2 to SMD0 bits in the UiMR register to “001b” (clock synchronous serial I/O mode)

(3) “1” (transmission enabled) is written to the TE bit in the UiC1 register, regardless of the TE bit

15.1.1.2 CLK Polarity Select Function

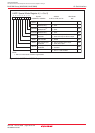

Use the CKPOL bit in the UiC0 register (i = 0 to 2) to select the transfer clock polarity. Figure 15.12

shows the polarity of the transfer clock.

(2) When the CKPOL bit in the UiC0 register = 1 (transmit data output at the rising

edge and the receive data taken in at the falling edge of the transfer clock)

D1 D2 D3 D4 D5 D6 D7

D1 D2 D3 D4 D5 D6 D7

D0

D0

TXDi

RXDi

CLKi

(1) When the CKPOL bit in the UiC0 register = 0 (transmit data output at the falling

edge and the receive data taken in at the rising edge of the transfer clock)

D1 D2 D3 D4 D5 D6 D7D0

D1 D2 D3 D4 D5 D6 D7D0

TXDi

RXDi

CLKi

* This applies to the case where the UFORM bit in the UiC0 register = 0

(LSB first) and the UiLCH bit in the UiC1 register = 0 (no reverse).

NOTES:

1. When not transferring, the CLKi pin outputs a high signal.

2. When not transferring, the CLKi pin outputs a low signal.

i = 0 to 2

(NOTE 1)

(NOTE 2)

Figure 15.12 Transfer Clock Polarity