Rev.2.00 Nov 28, 2005 page 60 of 378

REJ09B0124-0200

M16C/6N Group (M16C/6NK, M16C/6NM) 8. Clock Generating Circuit

Under development

This document is under development and its contents are subject to change.

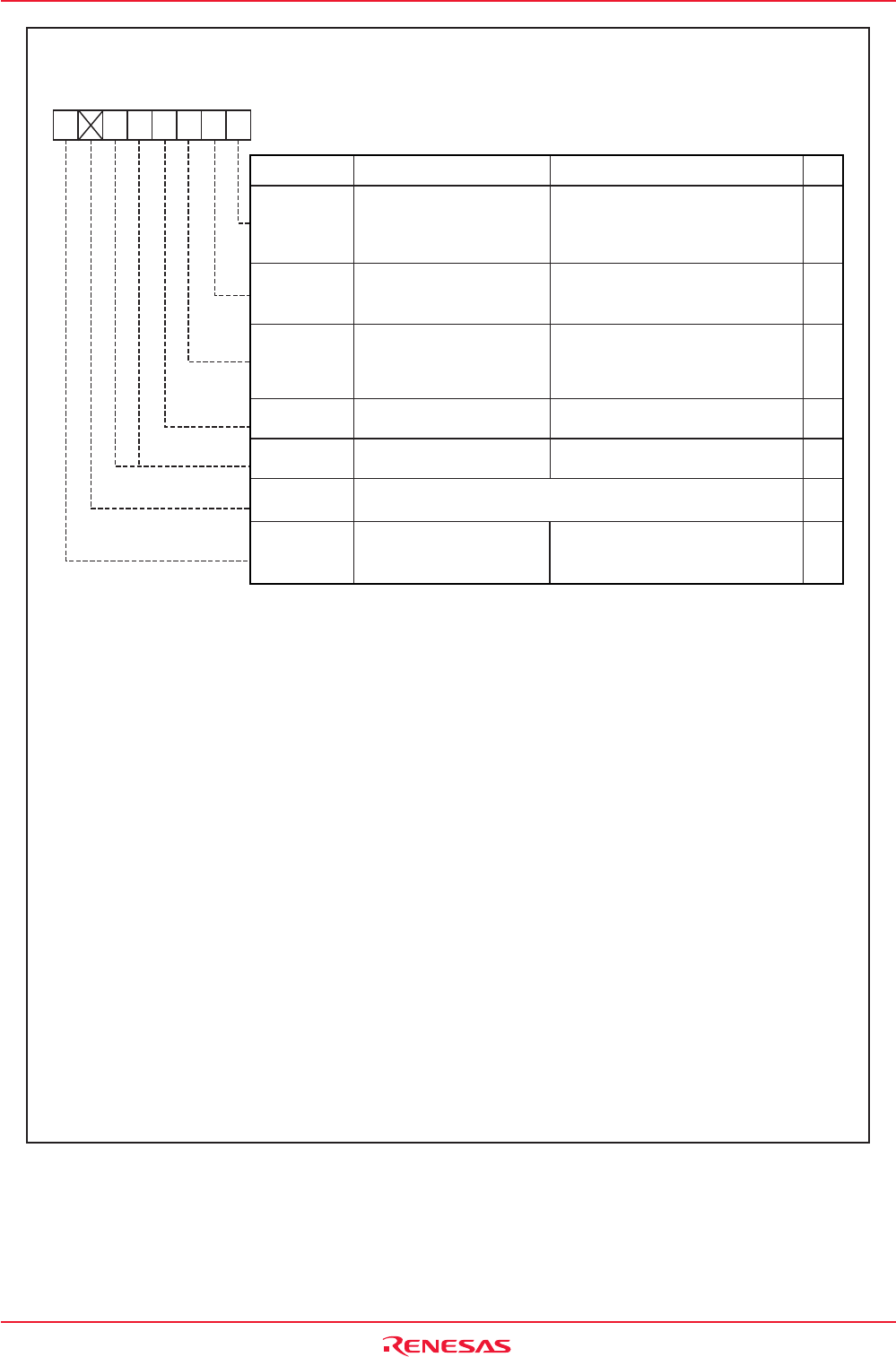

Figure 8.4 CM2 Register

Oscillation Stop Detection Register

(1)

Symbol

Address

After Reset

CM2 000Ch 0X000000b

(2)

Function

b7 b6 b5 b4 b3 b2 b1 b0

Bit Symbol

Bit Name

0 : Oscillation stop, re-oscillation

detection function disabled

1 : Oscillation stop, re-oscillation

detection function enabled

0 : Main clock or PLL clock

1 : On-chip oscillator clock

(On-chip oscillator oscillating)

CM20

CM21

CM22

0 : Main clock stop, re-oscillation

not detected

1 : Main clock stop, re-oscillation

detected

System Clock Select

Bit 2

(2) (5) (6) (7) (8) (11)

CM23

-

(b5-b4)

-

(b6)

XIN Monitor Flag

(10)

0 : Main clock oscillating

1 : Main clock turned off

CM27

Operation Select Bit

(

behavior if oscillation stop,

re-oscillation is detected)

(2)

0 : Oscillation stop detection reset

1 : Oscillation stop, re-oscillation

detection interrupt

Nothing is assigned. When write, set to "0".

When read, its content is indeterminate.

Reserved Bit Set to "0"

NOTES:

1. Write to this register after setting the PRC0 bit in the PRCR register to "1" (write enable).

2. The CM20, CM21 and CM27 bits do not change at oscillation stop detection reset.

3. Set the CM20 bit to "0" (disable) before entering stop mode. After exiting stop mode, set the CM20 bit back

to "1" (enable).

4. Set the CM20 bit to "0" (disable) before setting the CM05 bit in the CM0 register.

5. When the CM20 bit is "1" (oscillation stop, re-oscillation detection function enabled), the CM27 bit is "1"

(oscillation stop, re-oscillation detection interrupt), and the CPU clock source is the main clock, the CM21 bit

is set to "1" (on-chip oscillator clock) if the main clock stop is detected.

6. If the CM20 bit is "1" and the CM23 bit is "1" (main clock turned off), do not set the CM21 bit to "0".

7. Effective when the CM07 bit in the CM0 register is "0".

8. Where the CM20 bit is "1" (oscillation stop, re-oscillation detection function enabled), the CM27 bit is "1"

(oscillation stop, re-oscillation detection interrupt), and the CM11 bit is "1" (the CPU clock source is PLL clock),

the CM21 bit remains unchanged even when main clock stop is detected. If the CM22 bit is "0" under these

conditions, an oscillation stop, re-oscillation detection interrupt request is generated at main clock stop detection;

it is, therefore, necessary to set the CM21 bit to "1" (on-chip oscillator clock) inside the interrupt routine.

9. This bit is set to "1" when the main clock is detected to have stopped and when the main clock is detected to

have restarted oscillating. When this bit changes state from "0" to "1", an oscillation stop and re-oscillation

detection interrupt request is generated. Use this bit in an interrupt routine to discriminate the causes of

interrupts between the oscillation stop and re-oscillation detection interrupt and the watchdog timer interrupt.

This bit is set to "0" by writing "0" in a program. (Writing "1" has no effect. Nor is it set to "0" by an oscillation

stop and re-oscillation detection interrupt request acknowledged.)

If an oscillation stop or a re-oscillation is detected when the CM22 bit = 1, no oscillation stop and re-oscillation

detection interrupt requests are generated.

10. Read the CM23 bit in an oscillation stop and re-oscillation detection interrupt handling routine to determine

the main clock status.

11. When the CM21 bit = 0 (on-chip oscillator turned off) and the CM05 bit = 1 (main clock turned off), the CM06

bit is fixed to "1" (divide-by-8 mode) and the CM15 bit is fixed to "1" (drive capability High).

RW

RO

-

RW

RW

RW

RW

RW

00

Oscillation Stop,

Re-Oscillation Detection

Enable Bit

(2) (3) (4)

Oscillation Stop,

Re-Oscillation Detection

Flag

(9)