TMS320C6712D

FLOATINGĆPOINT DIGITAL SIGNAL PROCESSOR

SPRS293A − OCTOBER 2005 − REVISED NOVEMBER 2005

54

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443

power-down mode logic

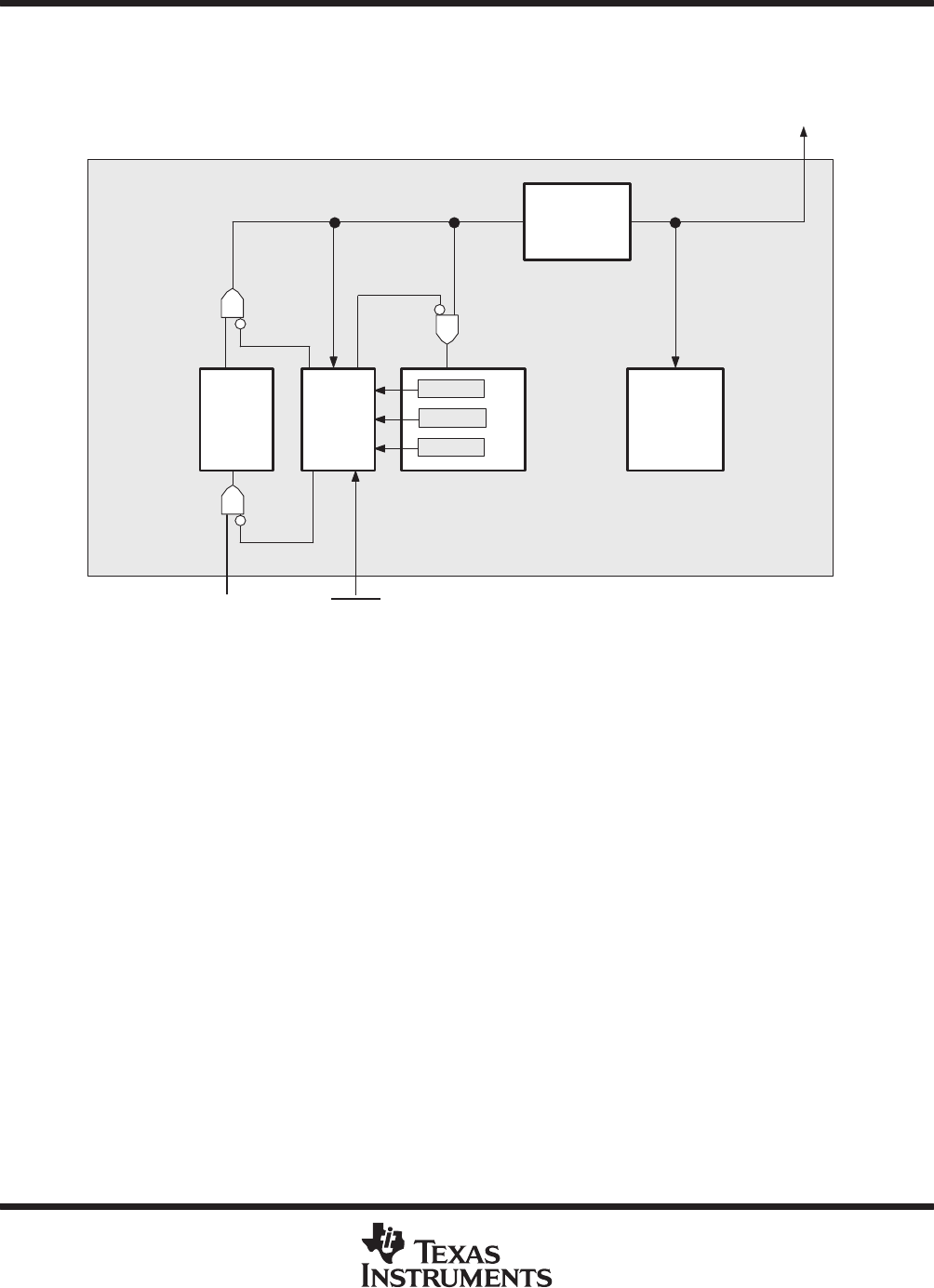

Figure 11 shows the power-down mode logic.

PWRD

Internal Clock Tree

CPU

IFR

IER

CSR

PD1

PD2

Power-

Down

Logic

Clock

PLL

CLKIN RESET

PD3

Internal

Peripherals

Clock

and Dividers

Distribution

†

External input clocks, with the exception of CLKOUT3 and CLKIN, are not gated by the power-down mode logic.

TMS320C6712D

CLKOUT2

Figure 11. Power-Down Mode Logic

†

triggering, wake-up, and effects

The power-down modes and their wake-up methods are programmed by setting the PWRD field (bits 15−10)

of the control status register (CSR). The PWRD field of the CSR is shown in Figure 12 and described in Table 32.

When writing to the CSR, all bits of the PWRD field should be set at the same time. Logic 0 should be used when

“writing” to the reserved bit (bit 15) of the PWRD field. The CSR is discussed in detail in the TMS320C6000 CPU

and Instruction Set Reference Guide (literature number SPRU189).