TMS320C6712D

FLOATINGĆPOINT DIGITAL SIGNAL PROCESSOR

SPRS293 − OCTOBER 2005

96

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443

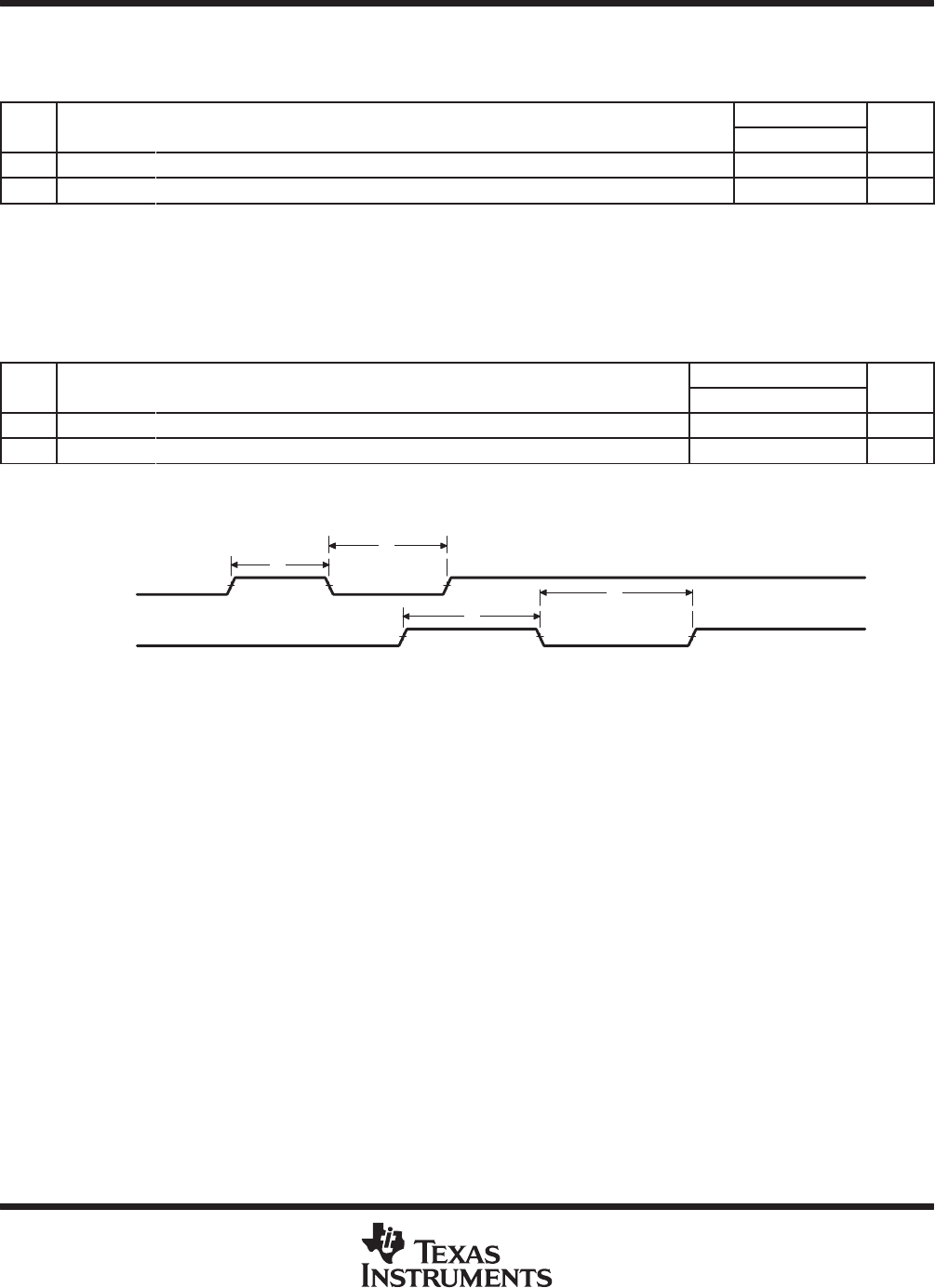

GENERAL-PURPOSE INPUT/OUTPUT (GPIO) PORT TIMING

timing requirements for GPIO inputs

†‡

(see Figure 48)

NO.

−150

UNIT

NO.

MIN MAX

UNIT

1 t

w(GPIH)

Pulse duration, GPIx high 4P ns

2 t

w(GPIL)

Pulse duration, GPIx low 4P ns

†

P = 1/CPU clock frequency in ns. For example, when running parts at 150 MHz, use P = 6.7 ns.

‡

The pulse width given is sufficient to generate a CPU interrupt or an EDMA event. However, if a user wants to have the DSP recognize the GPIx

changes through software polling of the GPIO register, the GPIx duration must be extended to at least 24P to allow the DSP enough time to access

the GPIO register through the CFGBUS.

switching characteristics over recommended operating conditions for GPIO outputs

†§

(see Figure 48)

NO.

PARAMETER

−150

UNIT

NO.

PARAMETER

MIN MAX

UNIT

3 t

w(GPOH)

Pulse duration, GPOx high 12P − 3 ns

4 t

w(GPOL)

Pulse duration, GPOx low 12P − 3 ns

†

P = 1/CPU clock frequency in ns. For example, when running parts at 150 MHz, use P = 6.7 ns.

§

The number of CFGBUS cycles between two back-to-back CFGBUS writes to the GPIO register is 12 SYSCLK1 cycles; therefore, the minimum

GPOx pulse width is 12P.

GPIx

GPOx

4

3

2

1

Figure 48. GPIO Port Timing