CY7C67200

Document #: 38-08014 Rev. *G Page 22 of 78

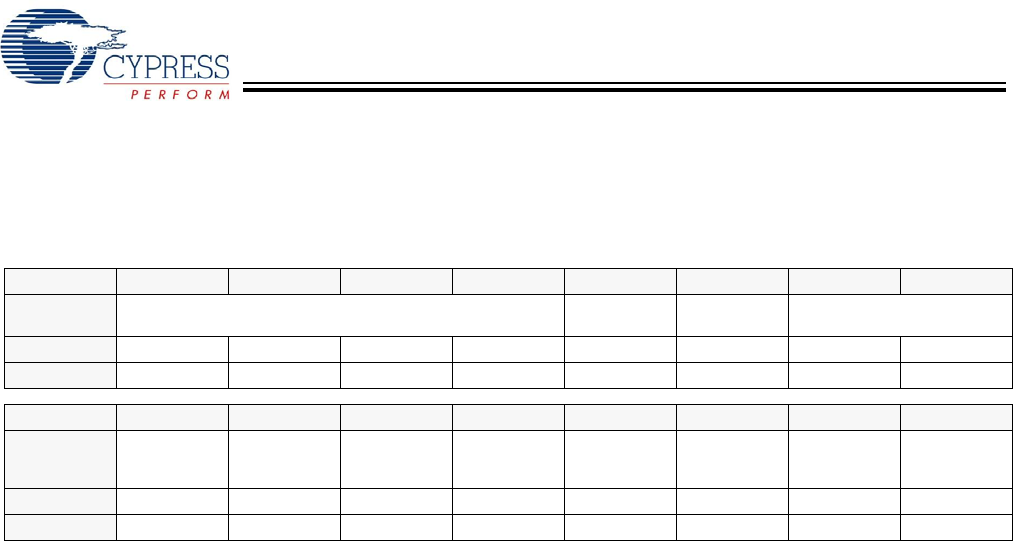

Host n Endpoint Status Register [R]

• Host 1 Endpoint Status Register 0xC086

• Host 2 Endpoint Status Register 0xC0A6

Figure 21. Host n Endpoint Status Register

Register Description

The Host n Endpoint Status register is a read-only register that

provides status for the last USB transaction.

Overflow Flag (Bit 11)

The Overflow Flag bit indicates that the received data in the

last data transaction exceeded the maximum length specified

in the Host n Count Register. The Overflow Flag should be

checked in response to a Length Exception signified by the

Length Exception Flag set to ‘1’.

1: Overflow condition occurred

0: Overflow condition did not occur

Underflow Flag (Bit 10)

The Underflow Flag bit indicates that the received data in the

last data transaction was less then the maximum length

specified in the Host n Count register. The Underflow Flag

should be checked in response to a Length Exception signified

by the Length Exception Flag set to ‘1’.

1: Underflow condition occurred

0: Underflow condition did not occur

Stall Flag (Bit 7)

The Stall Flag bit indicates that the peripheral device replied

with a Stall in the last transaction.

1: Device returned Stall

0: Device did not return Stall

NAK Flag (Bit 6)

The NAK Flag bit indicates that the peripheral device replied

with a NAK in the last transaction.

1: Device returned NAK

0: Device did not return NAK

Length Exception Flag (Bit 5)

The Length Exception Flag bit indicates the received data in

the data stage of the last transaction does not equal the

maximum Host Count specified in the Host n Count register. A

Length Exception can either mean an overflow or underflow

and the Overflow and Underflow flags (bits 11 and 10, respec-

tively) should be checked to determine which event occurred.

1: An overflow or underflow condition occurred

0: An overflow or underflow condition did not occur

Sequence Status (Bit 3)

The Sequence Status bit indicates the state of the last received

data toggle from the device. Firmware is responsible for

monitoring and handling the sequence status. The Sequence

bit is only valid if the ACK bit is set to ‘1’. The Sequence bit is

set to ‘0’ when an error is detected in the transaction and the

Error bit will be set.

1: DATA1

0: DATA0

Timeout Flag (Bit 2)

The Timeout Flag bit indicates if a timeout condition occurred

for the last transaction. A timeout condition can occur when a

device either takes too long to respond to a USB host request

or takes too long to respond with a handshake.

1: Timeout occurred

0: Timeout did not occur

Error Flag (Bit 1)

The Error Flag bit indicates a transaction failed for any reason

other than the following: Timeout, receiving a NAK, or

receiving a STALL. Overflow and Underflow are not

considered errors and do not affect this bit. CRC5 and CRC16

errors will result in an Error flag along with receiving incorrect

packet types.

1: Error detected

0: No error detected

Bit # 15 14 13 12 11 10 9 8

Field

Reserved Overflow

Flag

Underflow

Flag

Reserved

Read/Write - - - - R R - -

Default 0 0 0 0 0 0 0 0

Bit # 7 6 5 4 3 2 1 0

Field

Stall

Flag

NAK

Flag

Length

Exception

Flag

Reserved Sequence

Status

Timeout

Flag

Error

Flag

ACK

Flag

Read/Write R R R - R R R R

Default 0 0 0 0 0 0 0 0

[+] Feedback