CY7C67200

Document #: 38-08014 Rev. *G Page 24 of 78

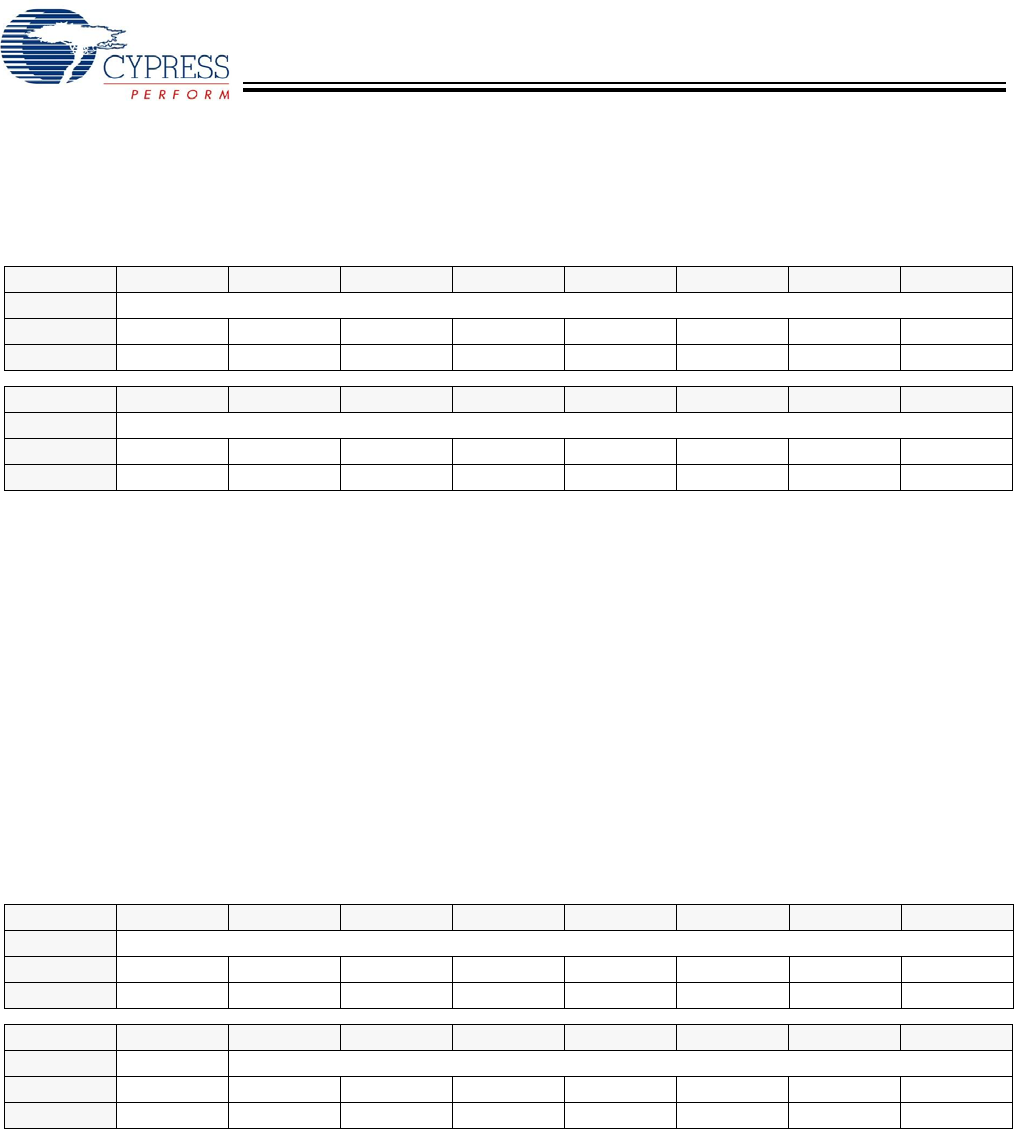

Host n Count Result Register [R]

• Host 1 Count Result Register 0xC088

• Host 2 Count Result Register 0xC0A8

Figure 23. Host n Count Result Register

Register Description

The Host n Count Result register is a read-only register that

contains the size difference in bytes between the Host Count

Value specified in the Host n Count register and the last packet

received. If an overflow or underflow condition occurs, that is

the received packet length differs from the value specified in

the Host n Count register, the Length Exception Flag bit in the

Host n Endpoint Status register will be set. The value in this

register is only valid when the Length Exception Flag bit is set

and the Error Flag bit is not set; both bits are in the Host n

Endpoint Status register.

Result (Bits [15:0])

The Result field contains the differences in bytes between the

received packet and the value specified in the Host n Count

register. If an overflow condition occurs, Result [15:10] is set

to ‘111111’, a 2’s complement value indicating the additional

byte count of the received packet. If an underflow condition

occurs, Result [15:0] indicates the excess byte count (number

of bytes not used).

Reserved

All reserved bits must be written as ‘0’.

Host n Device Address Register [W]

• Host 1 Device Address Register 0xC088

• Host 2 Device Address Register 0xC0A8

Figure 24. Host n Device Address Register

Register Description

The Host n Device Address register is a write-only register that

contains the USB Device Address that the host wishes to

communicate with.

Address (Bits [6:0])

The Address field contains the value of the USB address for

the next device that the host is going to communicate with.

This value must be written by firmware.

Reserved

All reserved bits must be written as ‘0’.

Bit # 15 14 13 12 11 10 9 8

Field Result...

Read/Write R R R R R R R R

Default 0 0 0 0 0 0 0 0

Bit # 7 6 5 4 3 2 1 0

Field ...Result

Read/Write R R R R R R R R

Default 0 0 0 0 0 0 0 0

Bit # 15 14 13 12 11 10 9 8

Field Reserved...

Read/Write - - - - - - - -

Default 0 0 0 0 0 0 0 0

Bit # 7 6 5 4 3 2 1 0

Field ...Reserved Address

Read/Write - W W W W W W W

Default 0 0 0 0 0 0 0 0

[+] Feedback