CY7C67200

Document #: 38-08014 Rev. *G Page 46 of 78

HSS Transmit Gap Register [0xC074] [R/W]

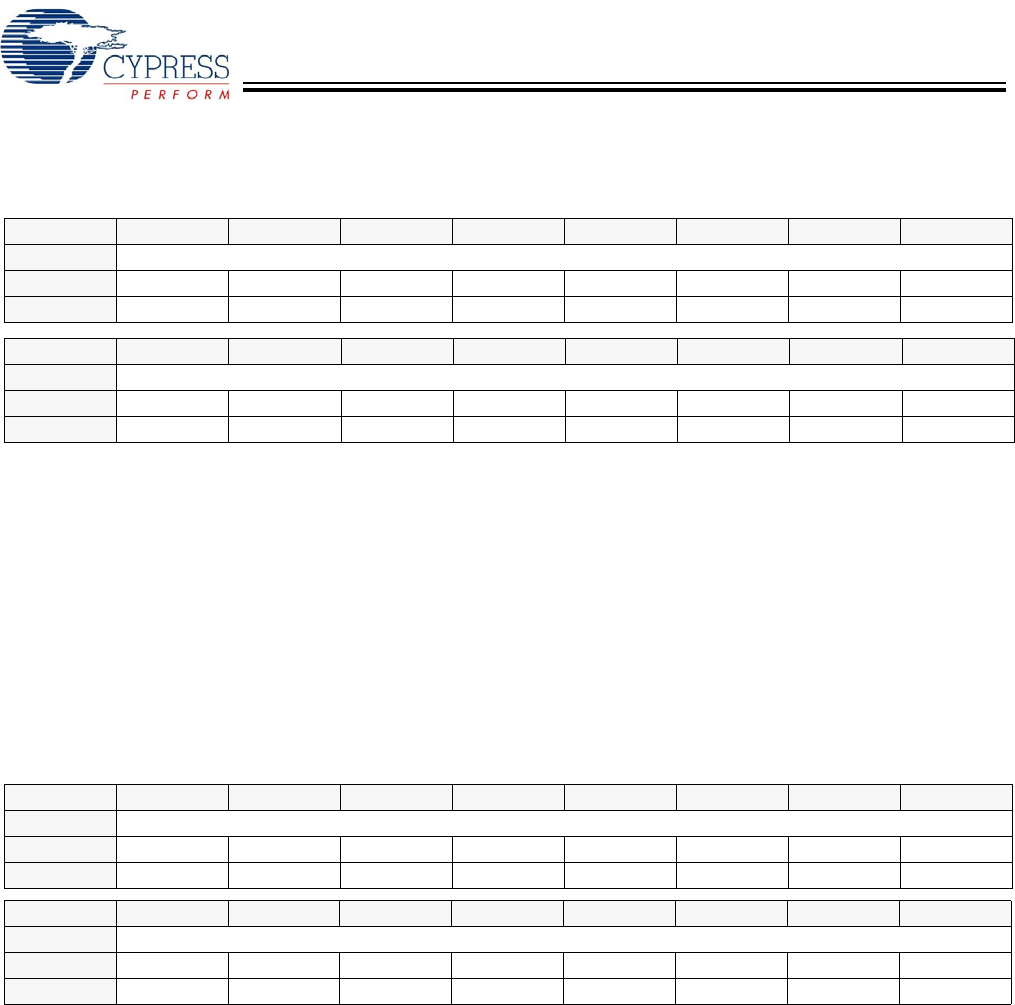

Figure 50. HSS Transmit Gap Register

Register Description

The HSS Transmit Gap register is only valid in block transmit mode. It allows for a programmable number of stop bits to be inserted

thus overwriting the One Stop Bit in the HSS Control register. The default reset value of this register is 0x0009, equivalent to two

stop bits.

Transmit Gap Select (Bits [7:0])

The Transmit Gap Select field sets the inactive time between transmitted bytes. The inactive time = (Transmit Gap Select – 7) *

bit time. Therefore an Transmit Gap Select Value of 8 is equal to having one Stop bit.

Reserved

All reserved bits must be written as ‘0’.

HSS Data Register [0xC076] [R/W]

Figure 51. HSS Data Register

Register Description

The HSS Data register contains data received on the HSS port (not for block receive mode) when read. This receive data is valid

when the Receive Ready bit of the HSS Control register is set to ‘1’. Writing to this register initiates a single byte transfer of data.

The Transmit Ready Flag in the HSS Control register must read ‘1’ before writing to this register (this avoids disrupting the

previous/current transmission).

Data (Bits [7:0])

The Data field contains the data received or to be transmitted on the HSS port.

Reserved

All reserved bits must be written as ‘0’.

Bit # 15 14 13 12 11 10 9 8

Field Reserved

Read/Write - - - - - - - -

Default 0 0 0 0 0 0 0 0

Bit # 7 6 5 4 3 2 1 0

Field Transmit Gap Select

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Default 0 0 0 0 1 0 0 1

Bit # 15 14 13 12 11 10 9 8

Field Reserved

Read/Write - - - - - - - -

Default X X X X X X X X

Bit # 7 6 5 4 3 2 1 0

Field Data

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Default X X X X X X X X

[+] Feedback