CY7C67200

Document #: 38-08014 Rev. *G Page 68 of 78

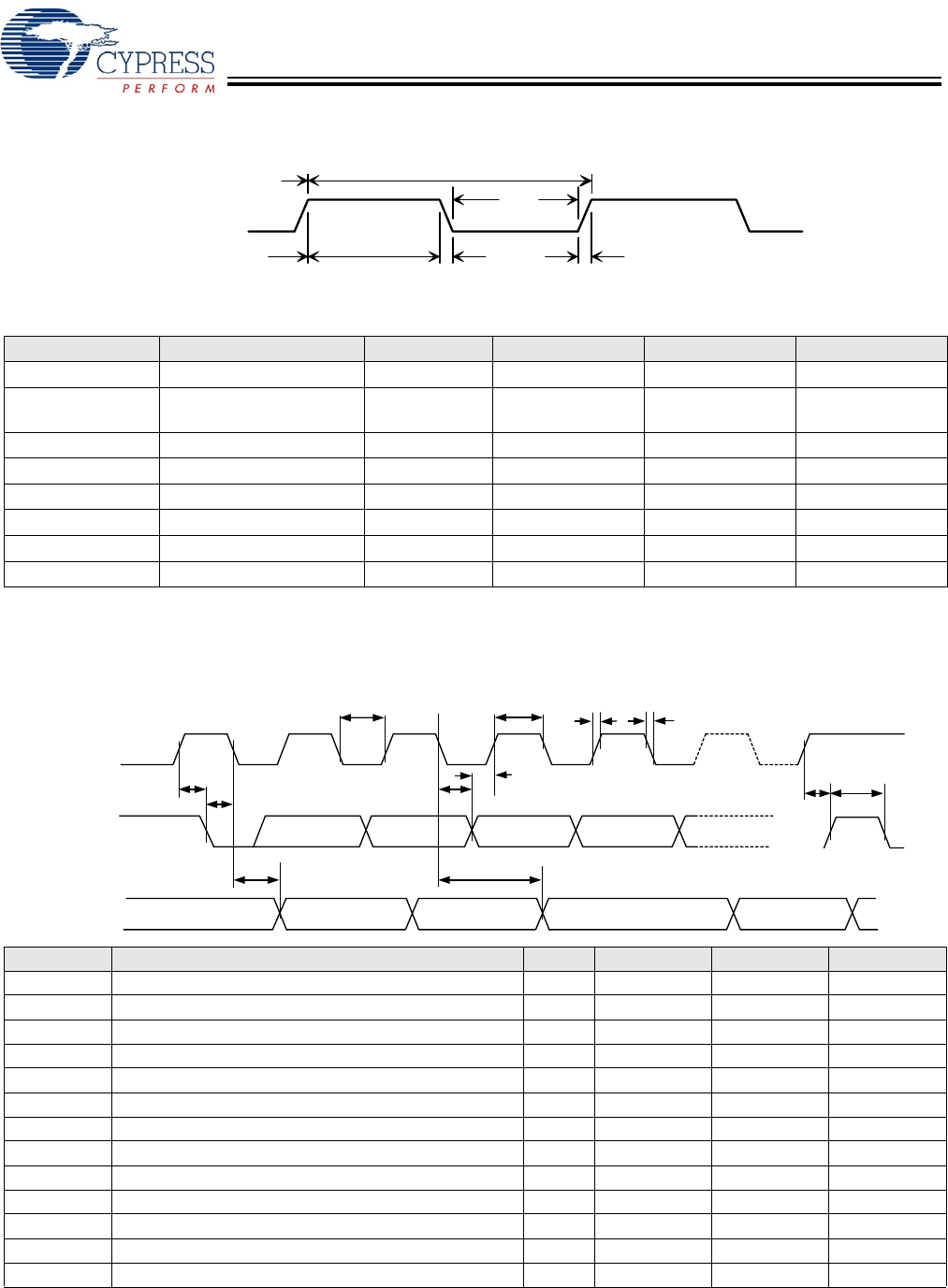

Clock Timing

I

2

C EEPROM Timing

Parameter Description Min. Typ. Max. Unit

f

CLK

Clock Frequency 12.0 MHz

v

XINH

[10]

Clock Input High

(XTALOUT left floating)

1.5 3.0 3.6 V

t

CLK

Clock Period 83.17 83.33 83.5 ns

t

HIGH

Clock High Time 36 44 ns

t

LOW

Clock Low Time 36 44 ns

t

RISE

Clock Rise Time 5.0 ns

t

FALL

Clock Fall Time 5.0 ns

Duty Cycle 45 55 %

XTALIN

Clock Timin

g

t

RISE

t

FALLt

HIGH

t

CLK

t

LOW

Parameter Description Min. Typical Max. Unit

f

SCL

Clock Frequency 400 kHz

t

LOW

Clock Pulse Width Low 1300 ns

t

HIGH

Clock Pulse Width High 600 ns

t

AA

Clock Low to Data Out Valid 900 ns

t

BUF

Bus Idle Before New Transmission 1300 ns

t

HD.STA

Start Hold Time 600 ns

t

SU.STA

Start Setup Time 600 ns

t

HD.DAT

Data In Hold Time 0 ns

t

SU.DAT

Data In Setup Time 100 ns

t

R

Input Rise Time 300 ns

t

F

Input Fall Time 300 ns

t

SU.STO

Stop Setup Time 600 ns

t

DH

Data Out Hold Time 0 ns

Note

10.

v

XINH

is required to be 3.0V to obtain an internal 50/50 duty cycle clock.

SCL

t

LOW

t

HIGH

t

R

t

HD.DAT

t

AA

t

DH

SDA IN

SDA OUT

1. I2C EEPROM Bus Timing - Serial I/O

t

SU.STA

t

HD.STA

t

F

t

SU.DAT t

BUF

t

SU.STO

[+] Feedback