CY7C67200

Document #: 38-08014 Rev. *G Page 27 of 78

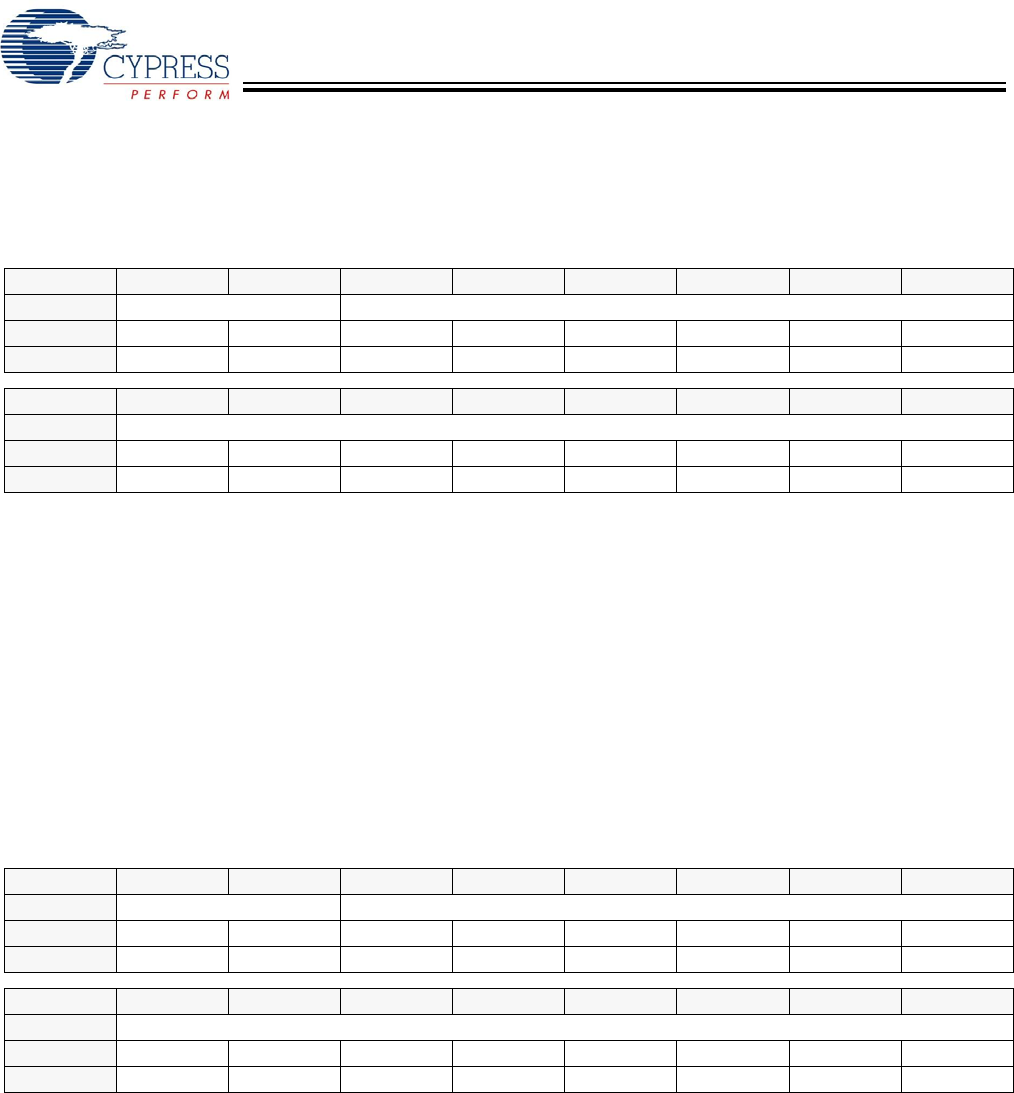

Host n SOF/EOP Count Register [R/W]

• Host 1 SOF/EOP Count Register 0xC092

• Host 2 SOF/EOP Count Register 0xC0B2

Figure 27. Host n SOF/EOP Count Register

Register Description

The Host n SOF/EOP Count register contains the SOF/EOP

Count Value that is loaded into the SOF/EOP counter. This

value is loaded each time the SOF/EOP counter counts down

to zero. The default value set in this register at power-up is

0x2EE0, which will generate a 1-ms time frame. The

SOF/EOP counter is a down counter decremented at a

12-MHz rate. When this register is read, the value returned is

the programmed SOF/EOP count value.

Count (Bits [13:0])

The Count field sets the SOF/EOP counter duration.

Reserved

All reserved bits must be written as ‘0’.

Host n SOF/EOP Counter Register [R]

• Host 1 SOF/EOP Counter Register 0xC094

• Host 2 SOF/EOP Counter Register 0xC0B4

Figure 28. Host n SOF/EOP Counter Register

Register Description

The Host n SOF/EOP Counter register contains the current

value of the SOF/EOP down counter. This value can be used

to determine the time remaining in the current frame.

Counter (Bits [13:0])

The Counter field contains the current value of the SOF/EOP

down counter.

Bit # 15 14 13 12 11 10 9 8

Field Reserved Count...

Read/Write - - R/W R/W R/W R/W R/W R/W

Default 0 0 1 0 1 1 1 0

Bit # 7 6 5 4 3 2 1 0

Field ...Count

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Default 1 1 1 0 0 0 0 0

Bit # 15 14 13 12 11 10 9 8

Field Reserved Counter...

Read/Write - - R R R R R R

Default X X X X X X X X

Bit # 7 6 5 4 3 2 1 0

Field ...Counter

Read/Write R R R R R R R R

Default X X X X X X X X

[+] Feedback