Intel

®

IXP45X and Intel

®

IXP46X Product Line of Network Processors

February 2007 HDD

Document Number: 305261; Revision: 004 35

General Hardware Design Considerations—Intel

®

IXP45X and Intel

®

IXP46X Product Line of

Network Processors

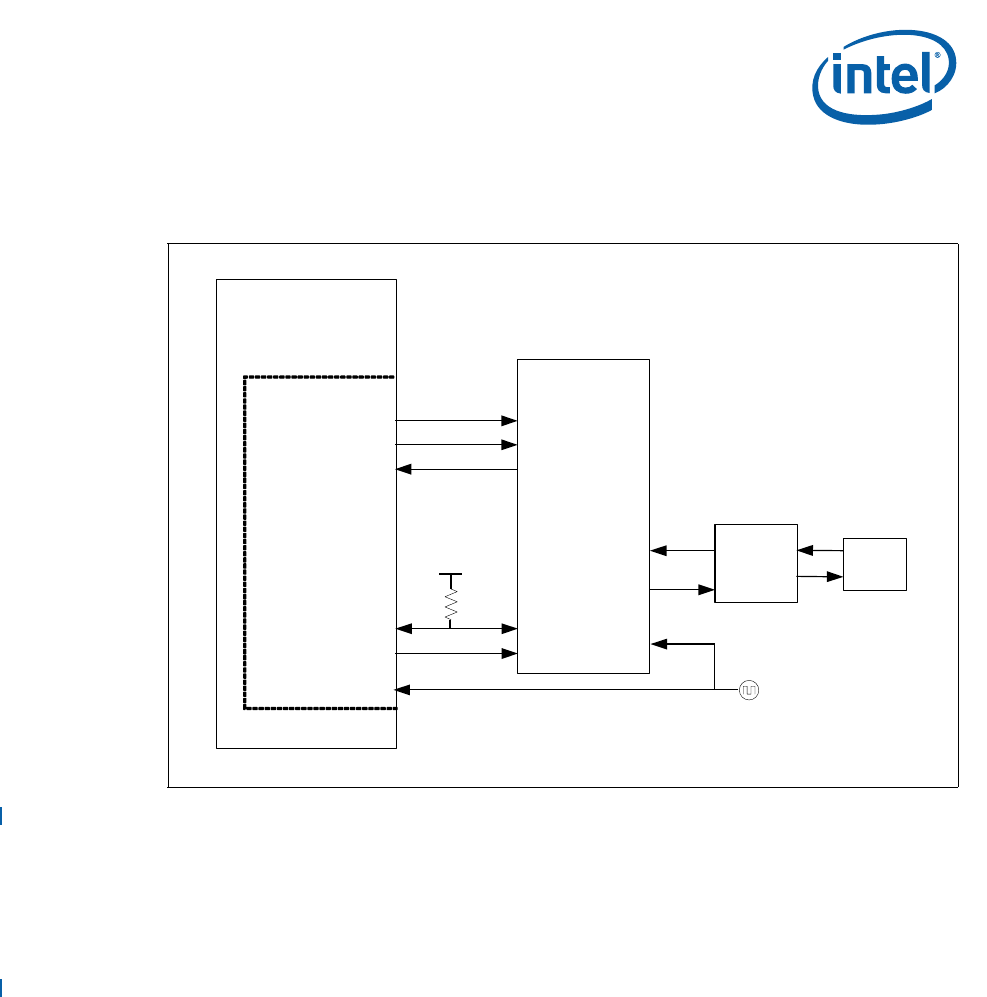

3.5.4 Device Connection, SMII

3.6 GPIO Interface

The IXP45X/IXP46X network processors provide 16 general-purpose input/output pins

for use in generating and capturing application specific input and output signals. Each

individual pin can be programmed as either an input or output.

When programmed as an input, GPIO0 through GPIO12 can be configured to be an

interrupt source. Interrupt sources can be configured to detect either active high,

active low, rising edge, falling edge, or transitional. In addition, GPIO14 and GPIO15

can be programmed to provide a user-programmable clock out.

During reset, all pins are configured as inputs and remain in this state until configured

otherwise, with the exception of GPIO15, which by default provides a clock output. The

driver strength of GPIO pins is sufficient to drive external LEDs with a proper limiting

resistor.

Figure 9. SMII Interface Example

Intel

®

IXP46X

Product Line

Network Processor

SMII Interface

Magnetics RJ45

125 MHz

REF CLK

SMII_RXDATA

SMII_TXDATA

SMII_TXSYNC

SMII_CLK

ETH_MDIO

ETH_MDC

RXDATA

TXDATA

MDIO

MDC

TXSYNC

10/100

PHY

VCC (3.3 V)

B4103-002

1.5 KΩ