Intel

®

IXP45X and Intel

®

IXP46X Product Line of Network Processors—Category

Intel

®

IXP45X and Intel

®

IXP46X Product Line of Network Processors

HDD February 2007

82 Document Number: 305261, Revision: 004

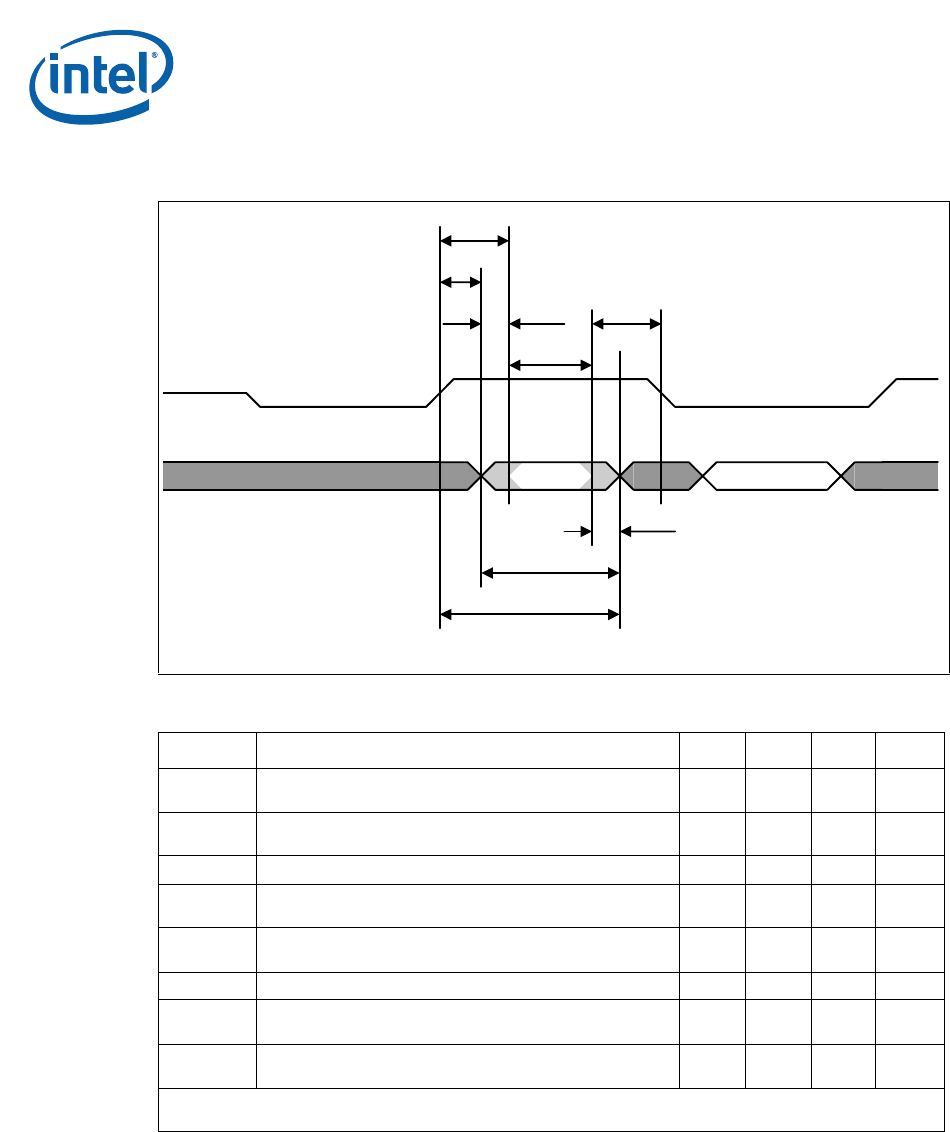

Figure 32. DDR Data to DQS Read Timing Parameters

Table 30. DDR Data to DQS Read Timing Parameters

Symbol Parameter Min Max Units Notes

T

1

IXP45X/IXP46X network processors delay for data group

valid after any edge of DQS

0.75 ns 1

T

2

IXP45X/IXP46X network processors guaranteed time

before data group begins to transition invalid prior to DQS

1.0 ns 1

T

3

Data valid window for IXP45X/IXP46X network processors 2.0 ns 1

T

4

DQ-DQS skew, DQS to last data group signal going valid

from DDR memory device

0.5 ns 1

T

5

DQ-DQS hold, DQS to first data group signal going non-

valid from DDR memory device

3.0 ns 1

T

6

Data valid window from DDR memory device 2.5 ns 1

T

7

Allowable data group to DQS difference for data going

valid (T

1

- T

4

)

0.25 ns 1

T

8

Allowable data group to DQS difference for data going

invalid (T

5

- T

3

- T

1

)

0.25 ns 1

Notes:

1. Data group signals consist of DDRI_DM[4:0], DDRI_DQ[31:0], and DDRI_CB[7:0].

DQS

T

1

T

4

T

5

T

2

D0 D1

Data

T

7

T

6

T

3

T

8

B3989-001