CBI/CGI Technical Reference

Chassis Plans A-9

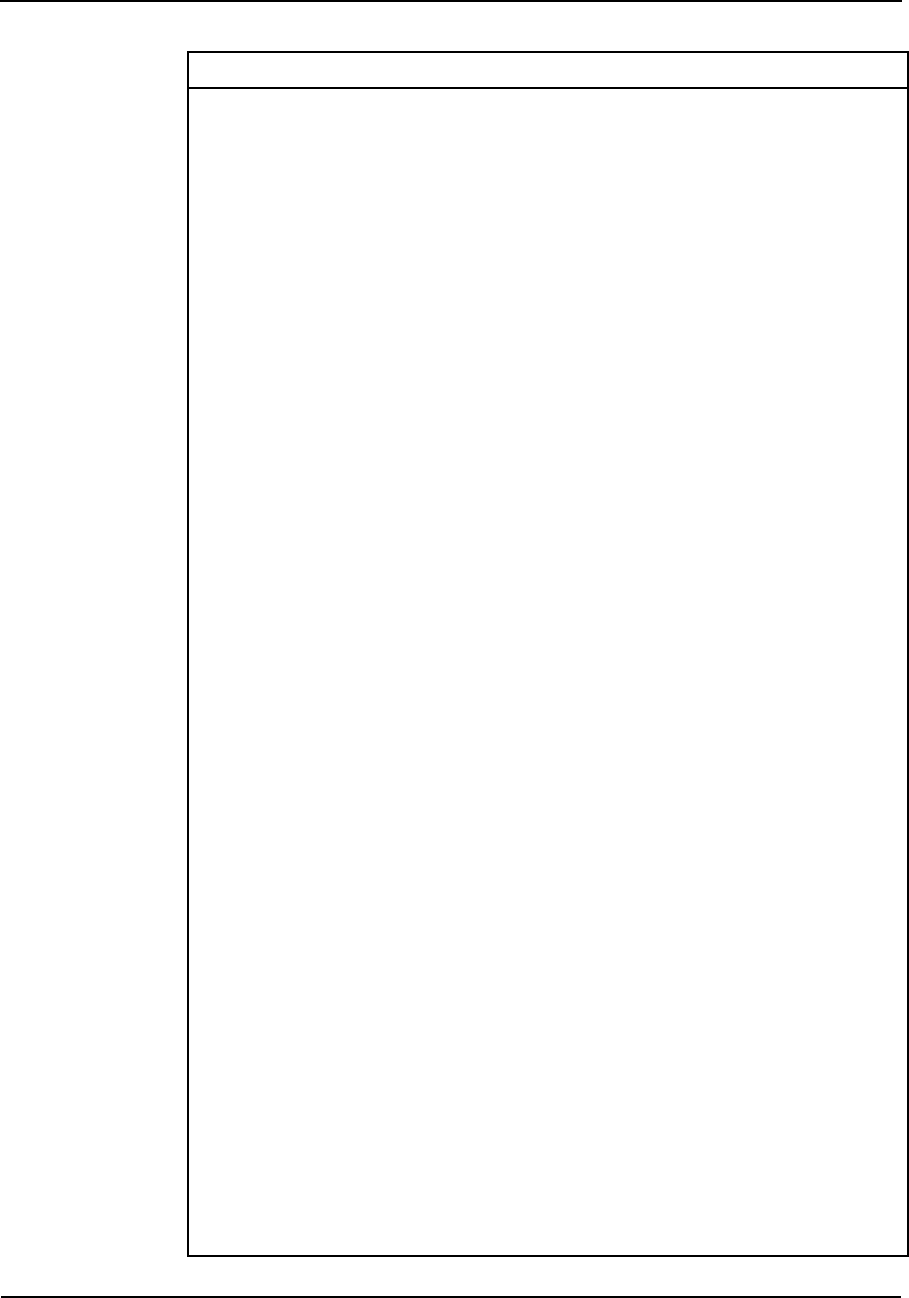

PORT 80 CODES

(

CONTINUED) Code Description

44

45

46

47

48

49

4B

4C

4D

4E

4F

50

51

52

53

54

57

58

59

interrupts enabled (if diagnostics switch is on). Initializing data to check memory

wraparound at 0:0 next.

Data initialized. Checking for memory wraparound at 0:0 and finding total system

memory size next.

Memory wraparound test done. Memory size calculation done. Writing patterns to test

memory next.

Memory pattern written to extended memory. Writing patterns to base 640KB memory

next.

Patterns written in base memory. Determining amount of memory below 1MB

memory next.

Amount of memory below 1MB found and verified. Determining amount of memory

above 1MB memory next.

Amount of memory above 1MB found and verified. Checking for soft reset and

clearing memory below 1MB for soft reset next. (If power-on situation, going to check-

point 4EH next.)

Memory below 1MB has been cleared via soft reset. Clearing memory above 1MB

next.

Memory above 1MB has been cleared via soft reset. Saving memory size next.

(Going to checkpoint 52H next.)

Memory test started, but not as result of soft reset. Displaying first 64KB memory

size next.

Memory size display started. Display is updated during memory test. Performing

sequential and random memory tests next.

Memory below 1MB has been tested and initialized. Adjusting displayed memory

size for relocation and shadowing next.

Memory size display adjusted for relocation and shadowing. Testing memory above

1MB next.

Memory above 1MB has been tested and initialized. Saving memory size information

next.

Memory size information and CPU registers are saved. Entering real mode next.

Shutdown was successful. CPU in real mode. Disabling Gate A20 line, parity and

NMI next.

A20 address line, parity and NMI are disabled. Adjusting memory size depending on

relocation and shadowing next.

Memory size adjusted for relocation and shadowing. Clearing “Hit <DEL>” message

next.

“Hit <DEL>” message cleared. “Wait...” message displayed. Starting DMA and

interrupt controller tests next.