KS152JB Universal Communications Controller

Technical Specifications

Kawasaki LSI USA, Inc. Page 100 of 120 Ver. 0.9 KS152JB2

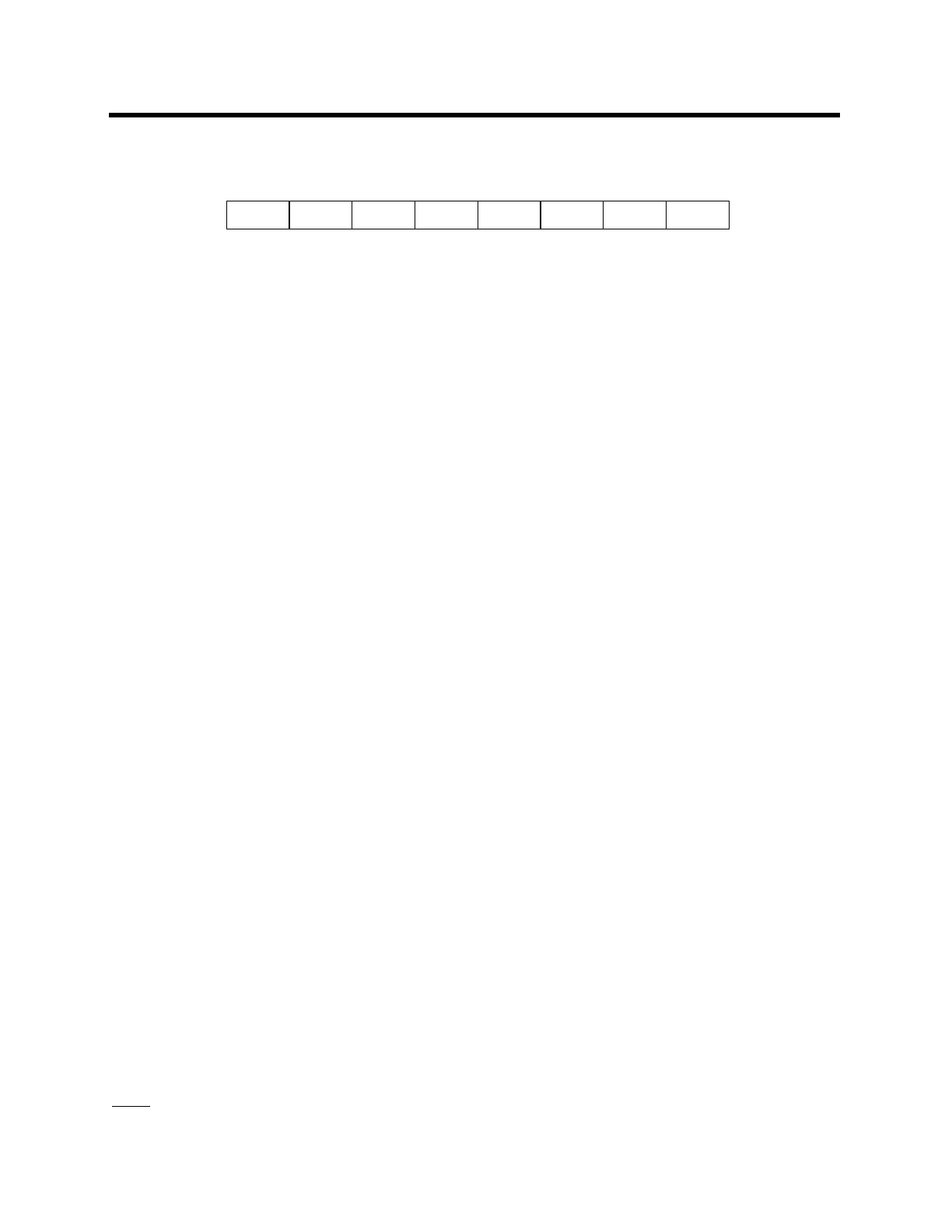

DCON0/1 (092H,093H)

The DCON register control the operation of the DMA channels by determining the source of data

to be transferred, the destination of the data to be transfer, and the various modes of operation.

DCON.0 (GO) - Enables DMA Transfer - When set it enables a DMA channel. If block mode is

set then DMA transfer starts as soon as possible under CPU control. If demand mode is set then

DMA transfer starts when a demand is asserted and recognized.

DCON.1 (DONE) - DMA Transfer is Complete - When set the DMA transfer is complete. It is set

when BCR equals 0 and is automatically reset when the DMA vectors to its interrupt routine. If

DMA interrupt is disabled and user software executes a jump on the DONE bit, then the user soft-

ware must also reset the done bit. If DONE bit is not set, then the DMA transfer is not complete.

DCON.2 (TM) - Transfer Mode - When set, DMA burst transfers are used if the DMA channel is

configured in the block mode or external interrupts are used to initiate a transfer if in Demand

Mode. When TM is cleared, Alternate cycle transfers are used if DMA is in the Block Mode, or

Local Serial Channel/GSC interrupts are used to initiate a transfer if in Demand Mode.

DCON.3 (DM) - DMA Channel Mode - When set, Demand Mode is used and when cleared Block

Mode is used.

DCON.4 (ISA) - Increment Source Address - When set, the source address registers are automat-

ically incremented during each transfer. When cleared the source registers are not incremented.

DCON.5 (SAS) - Source Address Space - When set the source of data for the DMA transfers is

internal data memory if autoincrement is also set. If auto increment is not set but SAS is, then the

source for the data will be one of the Special Function Register. When SAS is cleared, the source

for the data is external data memory.

DCON.6 (IDA) - Increment destination Address Space - When set, destination address registers

are incremented once after each byte is transferred. When cleared, the destination address regis-

ters are not automatically incremented.

DCON.7 (DAS) - Destination Address Space - When set, destination of data to be transferred is

internal data memory if autoincrement mode is also set. If auto increment is not set the destination

will be one of the Special Function Registers. When DAS is cleared then the destination is exter-

nal data memory

DCR - Deterministic Resolution, see MYSLOT.

DEN - An alternate function of one of the port 1 pins (P1.2). Its purpose is to enable external driv-

ers when the GSC is transmitting data. This function is always active when using the GSC and if

01234567

ISA DM

TM

DONE

GOSAS

IDADAS