KS152JB Universal Communications Controller

Technical Specifications

Kawasaki LSI USA, Inc. Page 39 of 120 Ver. 0.9 KS152JB2

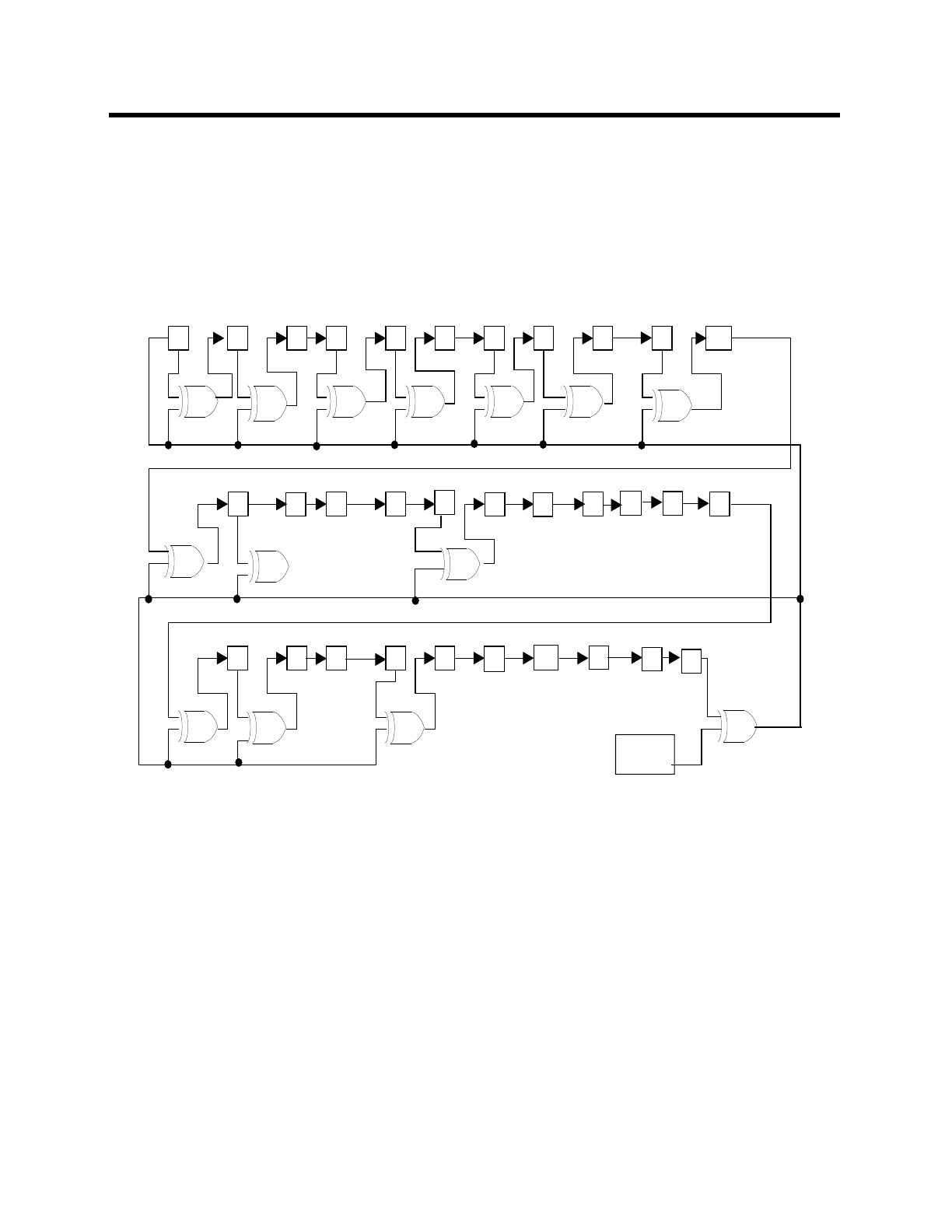

The CRC generator, as shown in figure below, operates by taking each bit as it is received and

XOR’ing it with bit 31 of the current CRC. This result is then placed in temporary storage. The

result of XOR’ing bit 31 with the received bit is then XOR’d with bits 0,

1,3,4,6,7,9,10,11,15,21,22,25 as the CRC is shifted right, the temporary storage space holding the

result of XOR’ing bit 31 and the incoming bit is shifted into position 0. The whole process is then

repeated with the next incoming or outgoing bit.

The user has no access to the CRC generator or the bits which constitute the CRC while in

CSMA/CD. On transmission, the CRC is automatically appended to the data being sent, and on

reception, the CRC bits are not normally loaded into the receive FIFO. Instead, they are automati-

cally stripped. The only indication the user has for the status of the CRC is a pass/fail flag. The

pass/fail flag only operates during reception. A CRC is considered as passing when the CRC gen-

erator has 11000111 00000100 11011010 01111011 B as a remainder after all of the data, includ-

ing the CRC checksum, from the transmitting station has been cycled through the CRC generator.

The preamble, BOF and EOF are not included as part of the CRC algorithm. An interrupt is avail-

able that will interrupt the CPU if the CRC of the receiver is invalid. The user can enable the CRC

to be passed to the CPU by placing the receiver in the raw receive mode.

This method of calculating the CRC is compatible with IEEE 802.3

EOF - The End of Frame indicates when the transmission is completed. The end flag in CSMA/

CD consists of an idle condition. An idle condition is assumed when there is no transitions and the

01

23

456

7

8

9

10

11

12

13

14

15

16

17

18

19 20

21

22

23

24 25

26

27

28

29

30

Received

bit