KS152JB Universal Communications Controller

Technical Specifications

Kawasaki LSI USA, Inc. Page 85 of 120 Ver. 0.9 KS152JB2

When the arbiter wants to DMA the XRAM, it first activates DMXRQ. This signal prevents Q2

from being set if it is not already set.An output low from Q2 enables the arbiter to carry out its

DMA to XRAM, and maintains an output high at

HLDA. When the arbiter completes its DMA,

the signal DMXRQ goes to O, which enables Q2 to accept signals from the

HLD input again.

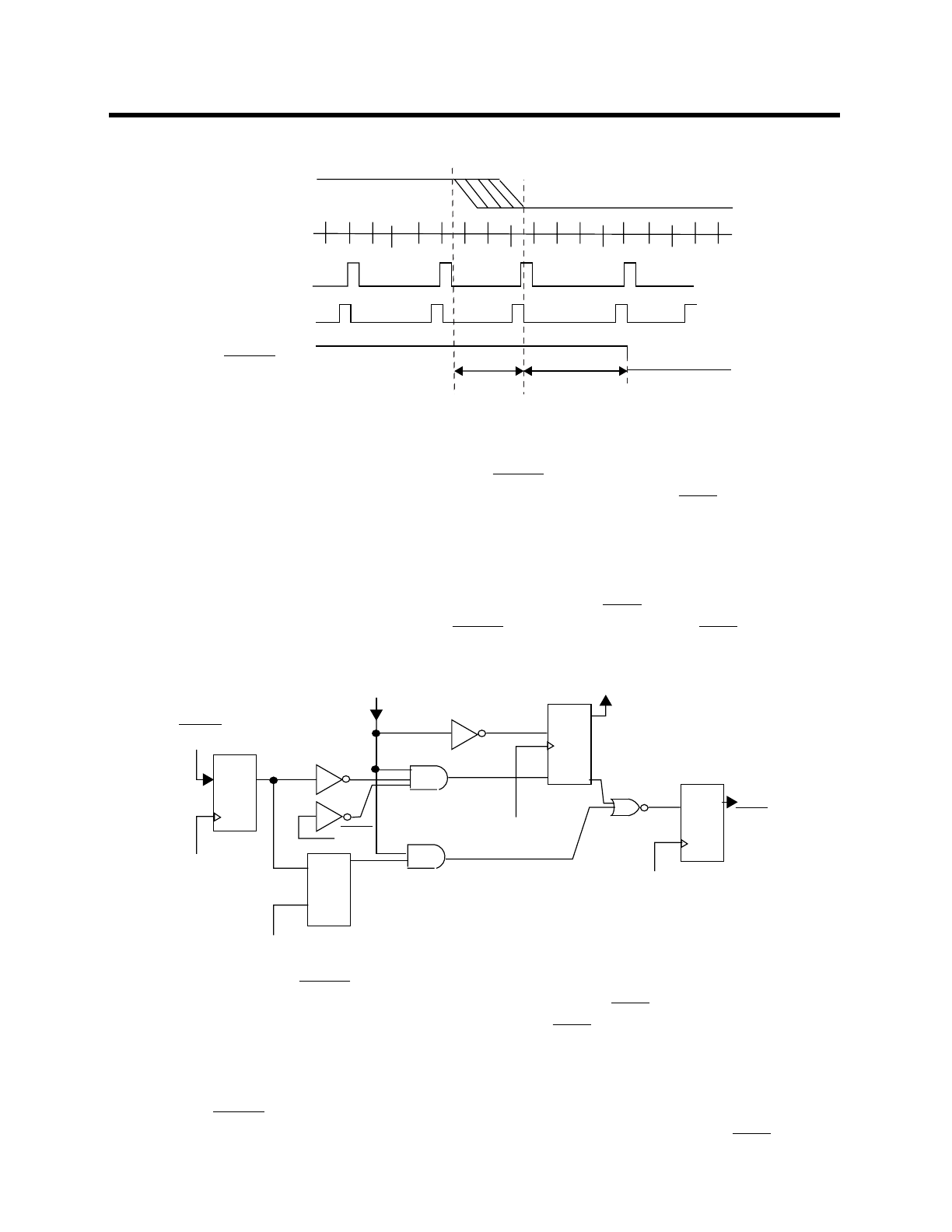

4.3.5 Internal Logic of the Requester

The internal logic of the requester is shown below. Initially, the requester’s internal signal

DMXRQ (DMA to XRAM Request) is at 0, so Q2 is set and the

HLD output is high. As long as

Q2 to be cleared (but doesn’t clear it), and, if

HLDA is high, also activates the HLD output.

A 1-to-0 transition from HLDA can now clear Q2, which will enable the requester to commence

its DMA to XRAM. Q2 being low also maintains an output low at

HLD. When the DMA is com-

pleted, DMXRQ goes to 0, which sets Q2 and de-activates

HLD.

Only DMXRQ going to 0 can set Q2. That means once Q2 gets cleared, enabling the requester’s

DMA to proceed, the arbiter has no way to stop the requester’s DMA in progress. At this point,

de-activating

HLDA will have no effect on the requester’s use of the bus. Only the requester itself

can stop the DMA in progress, and when it does, it de-activates both DMXRQ and

HLD.

HLD Input

CPU Osc.

Periods

Clock 1

Clock 2

HLDA Output

2 Osc.

Periods

4 Osc.

Periods

HLDA

Clock 1

DQ

Q1

DMXRQ

Clock 2

Clock 1

D

Q

Q3

HLD

S

Q

Q2

R

Q

Inhibit Requester’s DMA to XRAM

HLD

(Q3)

D

Q

Q1A

Clock 2