KS152JB Universal Communications Controller

Technical Specifications

Kawasaki LSI USA, Inc. Page 34 of 120 Ver. 0.9 KS152JB2

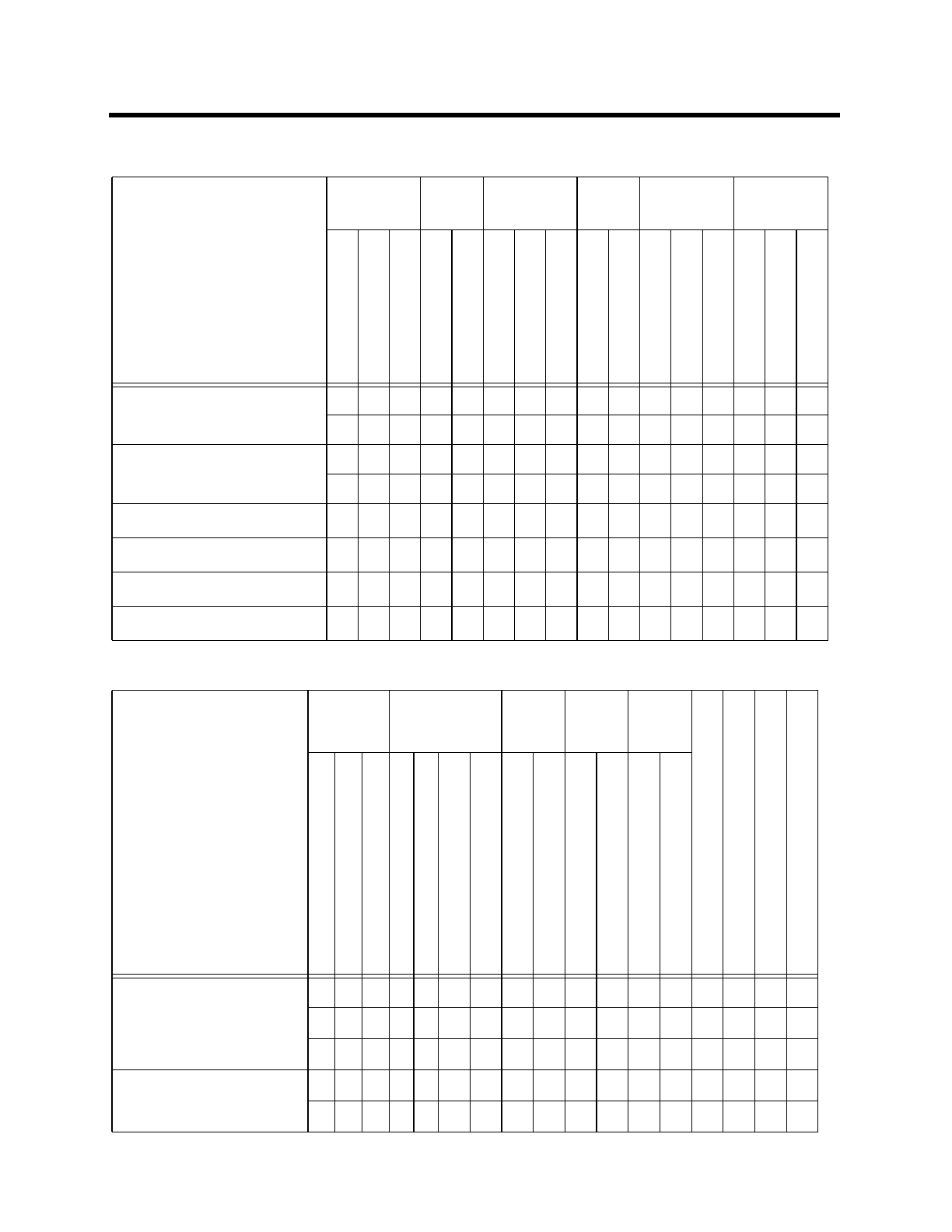

External clock

Internal clock

NMNOONOOOOONOOOO

OONOOOOOOOOOOOOO

Control cpu

Control dma

OOOOO1 OOOOOOOOOO

OOOOO1 OOOOOOOOOO

Raw Receive

111111111N111111

Raw Transmit

111111111N111111

CSMA

ONN1 P1 OOMNOOOOOO

SDLC

NOOP1 1 OOOOONOOOO

Table 10:

N-Not available.

M-Mandatory.

O-Optional.

P-Normally Preferred

X-N/A

backoff

preamble Jam Clock

contr

ol

r

a

w

tr

a

n

s

m

it

r

a

w

r

e

c

e

i

v

e

c

s

m

a

/

c

d

s

d

l

c

n

o

r

m

a

l

a

lt

e

r

n

a

t

e

d

e

t

e

r

m

i

n

i

s

ti

c

n

o

n

e

8

b

i

t

3

2

b

it

6

4

b

it

d

c

c

r

c

/

e

x

t

e

r

n

a

l

i

n

t

e

r

n

a

l

c

p

u

d

m

a

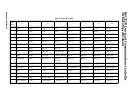

Manchester (csma/cd)

NRZI (sdlc)

NRZ (ext clock)

OOO

NOOOOONMOOOOMN

NNN

OOOONNNMOOOONM

OOO

OOOOOOMNOOOOOO

Flags:01111110(sdlc)

11/IDLE

NNN

OOOONNOOOOO1 1 P

OOO

1OOOOOOOOOO1 P1

Table 9:

N-Not available.

M-Mandatory.

O-Optional.

P-Normally Preferred

X-N/A

Data Flags CRC Duplex Ack

Addr

recognition

m

a

n

c

h

ec

st

er

nr

z

nr

zi

0

1

1

1

1

1

1

0

1

1/

id

le

n

o

n

e

1

6-

bi

t

cc

it

3

2

bi

ta

ut

o

h

al

f

d

u

pl

e

x

fu

ll

d

u

pl

e

x

n

o

n

e

h

ar

d

w

ar

e

us

er

d

ef

n

o

n

e/

al

l

8

bi

t

1

6

bi

t