KS152JB Universal Communications Controller

Technical Specifications

Kawasaki LSI USA, Inc. Page 16 of 120 Ver. 0.9 KS152JB2

case of level triggered interrupt, the IE0 and IE1 flags are not cleared and will have to be cleared

by the software. This is because in the level activated mode, it is the external requesting source

that controls the interrupt flag bit rather than the on-chip hardware.

The Timer 0 and 1 Interrupts are generated by the TF0 and TF1 flags. These flags are set by the

overflow in the Timer 0 and Timer 1. The TF0 and TF1 flags are automatically cleared by the

hardware when the timer interrupt is serviced.

The Timer 0 and 1 flags are set in S5P2 of the machine cycle in which the overflow occurs. The

values are polled in the next cycle.

The Local Serial block can generated interrupts on reception or transmission. There is however

only one interrupt source from the Local Serial block, which is obtained by oring the RI and TI

bits in the SCON SFR. These bits are not automatically cleared by the hardware and the user will

have to clear these bits using software.

All the bits that generate interrupts can be set or reset by hardware and thereby software initiated

interrupts can be generated. Each of the individual interrupts can be enabled or disabled by setting

or clearing a bit in the IE SFR. IE also has a global enable/disable bit EA, which can be cleared to

disable all the interrupts at once.

Priority Level Structure

There are two priority levels for the interrupts. Each interrupt source can be individually set to

either one of the two levels. Naturally, a higher priority interrupt cannot be interrupted by a lower

priority interrupt. However there exists a predefined hierarchy amongst the interrupts themselves.

This hierarchy comes into play when the interrupt controller has to resolve simultaneous requests

having the same priority level. This hierarchy is defined as shown below, the interrupts are num-

bered starting from the highest priority to the lowest.

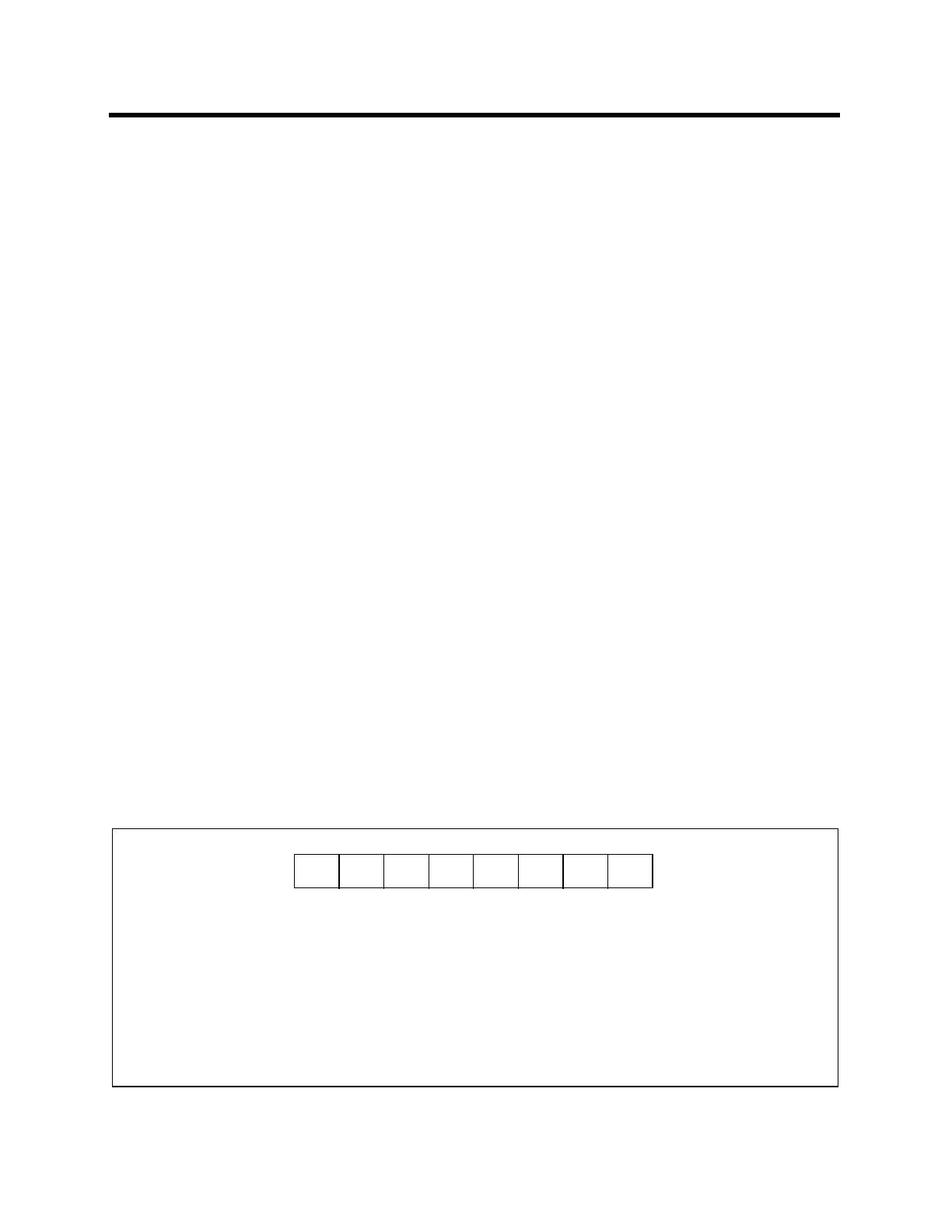

-- -- -- PS PT1 PX1 PT0 PX0

76543210

IE: Interrupt Enable Register.

reserved.--

PX0

PT0

PX1

PT1

PS

External interrupt 0 priority bit

Timer 0 interrupt priority bit.

External interrupt 1 priority bit.

Timer 1 interrupt priority bit.

Local Serial port interrupt priority bit.