KS152JB Universal Communications Controller

Technical Specifications

Kawasaki LSI USA, Inc. Page 103 of 120 Ver. 0.9 KS152JB2

added to the 8051BH core to accomplish high-speed transfers of packetized serial data.

GTxD - GSC Transmit Data output, an alternate function of one of the port 1 pins (P1.1). This pin

is used as the transmit output for the GSC. P1.1 must be programmed to a 1 for this function to

operate.

HBAEN - Hard Ware Based Acknowledge Enable, see RSTAT.

HLDA - Hold Acknowledge, an alternate function of one of the port 1 pins (P1.6). This pin is

used to perform the “HOLD ACKNOWLEDGE” function for DMA transfers. HLDA can be an

input or an output, depending on the configuration of the DMA channels. P1.6 must be pro-

grammed to a logic 1 for this function to operate.

HOLD - Hold, an alternate function of one of the port 1 pins (P1.5). This pin is used to perform

the “HOLD” function for the DMA transfers. HOLD can be an input or an output, depending on

the configuration of the DMA channels. P1.5 must be programmed to a logic 1 for this function to

operate.

IDA - Increment Destination Address, see DCON0.

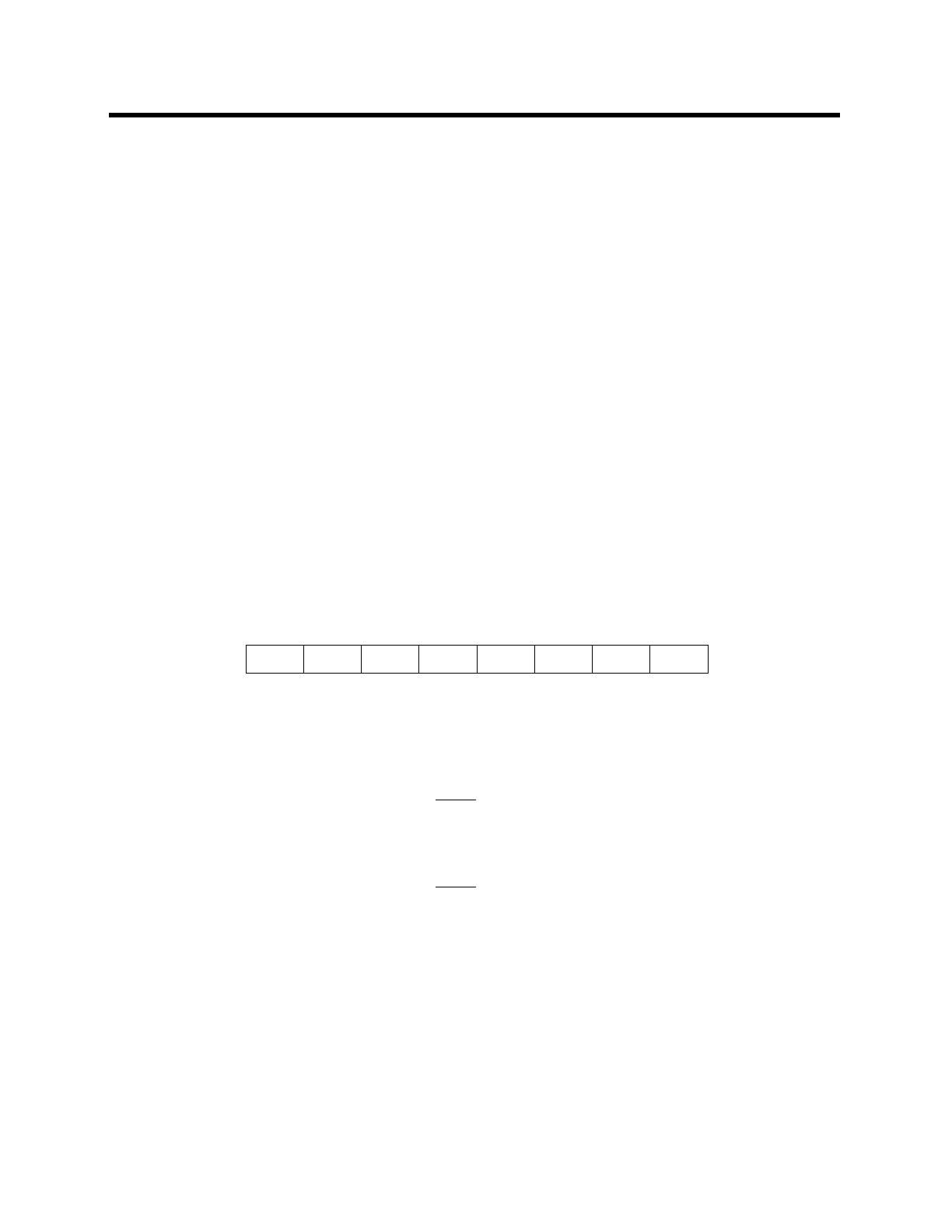

IE (0A8H)

Interrupt Enable SFR, used to individually enable the Timer and Local Serial Channel interrupts.

Also contains the global enable bit which must be set to a 1 to enable any interrupt to be automat-

ically recognized by the CPU.

IE.0 (EX0) - Enables the external interrupt

INT0 on P3.2.

IE.1 (ET0) - Enables the Timer0 interrupt.

IE.2 (EX1) - Enables the external interrupt

INT1 on P3.3.

IE.3 (ET1) - Enables the Timer 1 interrupt.

IE.4 (ES) - Enable the Local Serial Channel interrupt.

IE.7 (EA) - The global interrupt enable bit. This bit must be set to a 1 for any other interrupt to be

enabled.

01234567

EA

ES ET1 EX1 ET0 EX0