KS152JB Universal Communications Controller

Technical Specifications

Kawasaki LSI USA, Inc. Page 104 of 120 Ver. 0.9 KS152JB2

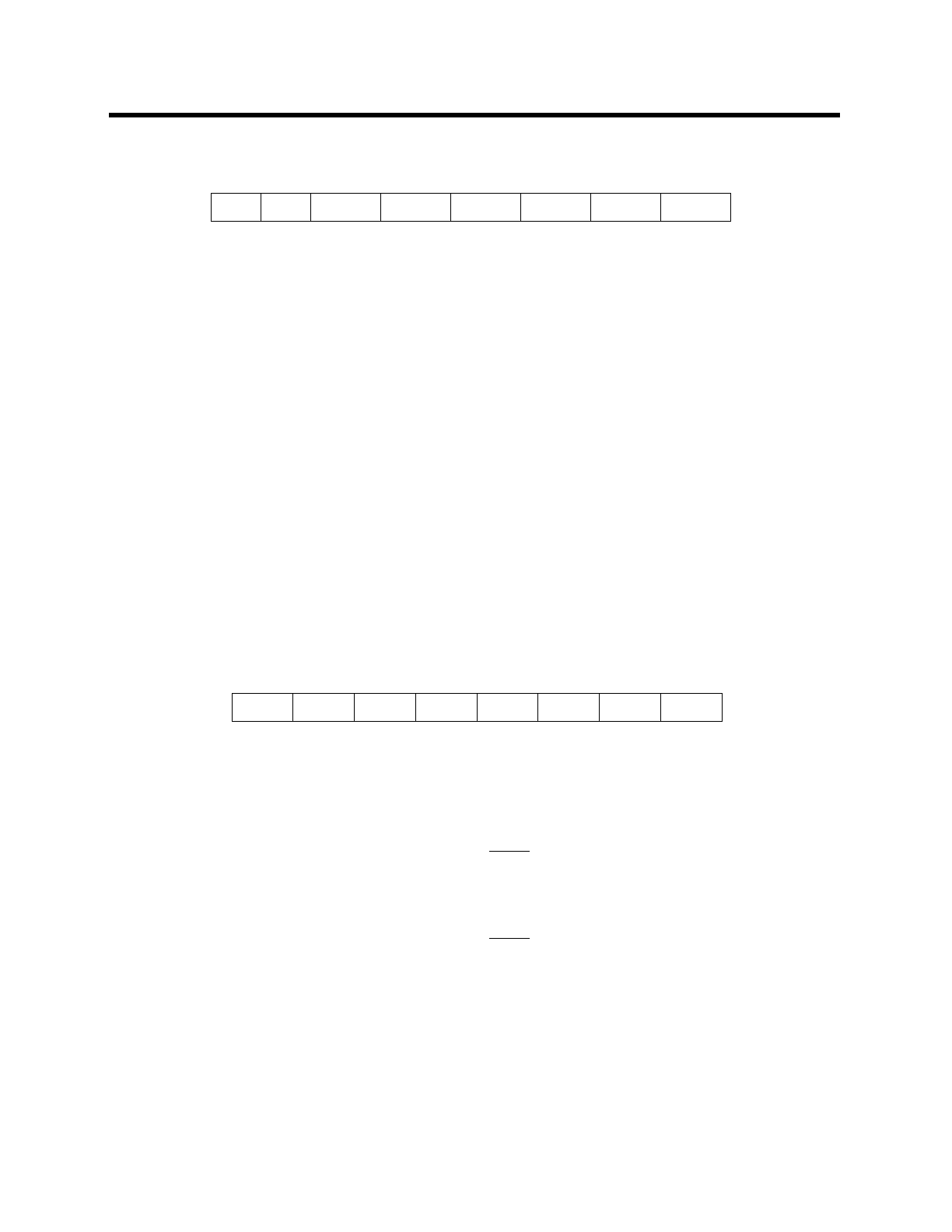

IEN1 (0C8H)

Interrupt enable register for DMA and GSC interrupts. A 1 in any bit position enables that interrupt.

IEN1.0 (EGSRV) - Enables the GSC valid receive interrupt.

IEN1.1 (EGSRE) - Enables the GSC receive error interrupt.

IEN1.2 (EDMA0) - Enables the DMA done interrupt for channel 0.

IEN1.3 (EGSTV) - Enables the GSC valid transmit interrupt.

IEN1.4 (EDMA1) - Enables the DMA done interrupt for Channel1.

IEN1.5 (EGSTE) - Enables the GSC transmit error interrupt.

IFS - (0A4H) Interframe Space, determines the number of bit times separating transmitted frames

in CSMA/CD and SDLC.

IP (0B8H)

Allows the user software two levels of prioritization to be assigned to each of the interrupts in IE.

A 1 assigns the corresponding interrupt in IE a higher interrupt than an interrupt with a correspond-

ing 0.

IP.0 (PX0) - Assigns priority of external interrupt,

INT0.

IP.1 (PT0) - Assigns the priority of Timer 0 interrupt, T0.

IP.2 (PX1) - Assigns priority of external interrupt,

INT1.

IP.3 (PT1) - Assigns the priority of Timer1 interrupt, T1.

IP.4 (PS) - Assigns the priority of the LSC interrupt, SBUF.

01234567

EDMA1 EGSTV EDMA0 EGSRE EGSRVEGSTE

01234567

PS PT1 PX1 PT0 EX0