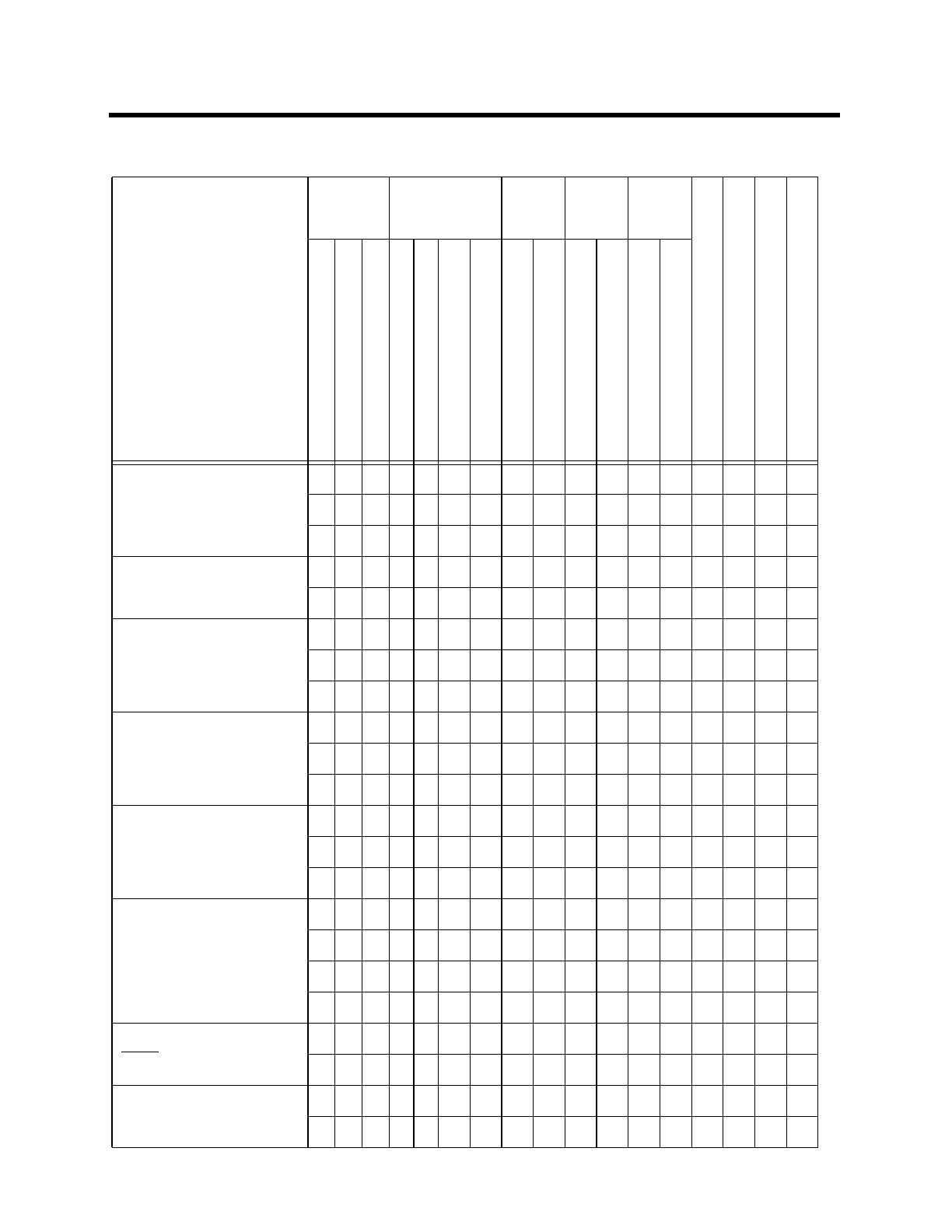

KS152JB Universal Communications Controller

Technical Specifications

Kawasaki LSI USA, Inc. Page 35 of 120 Ver. 0.9 KS152JB2

CRC: NONE

16-bit CCITT

32-bitAUTODIN II

NNN

1111NN11111111

OOO

OOOOOOOOOO1 1 OO

OOO

OOOOOOOOOO1 1 OO

Half Duples

Full Duplex

OOO

OOOOOOOOOOOOOO

NNN

OOOONNOOOONNNP

Acknowledge: None

Hardware

User defined.

OOO

OOOOOOOOOOOOOO

NOO

NOOOOONOOONNON

OOO

OOOOOOOOOOOOO1

Address recog: none

8-bit

16 bit

OOO

OOOOOOOOOOOOOO

OOO

OOOOOOOOOO1 1 OO

OOO

OOOOOOOOOO1 1 OO

Coll resol: Normal

Alternate

Deterministic

XNN

NOOOOONOOOONMN

NXN

NOOOOONOOOONMN

NNX

NOOOOONOOOONMN

Preamble: None

8-bit

32-bit

64-bit

NNN

XNNNNNOOOOOONP

OOO

NXNNOOOOOO1 1 OO

OOO

NNXNOOOOOO1 1 OO

OOO

NNNXOOOOOONNOO

DC JAM

CRC JAM

OOO

NOOOXNNOOOONMN

OOO

NOOONXNOOOONMN

External clock

Internal clock

NNN

OOOONNXNOOOONO

OOO

OOOOOONXOOOOOO

Table 10:

N-Not available.

M-Mandatory.

O-Optional.

P-Normally Preferred

X-N/A

backoff

preamble Jam Clock

contr

ol

r

a

w

tr

a

n

s

m

it

r

a

w

r

e

c

e

i

v

e

c

s

m

a

/

c

d

s

d

l

c

n

o

r

m

a

l

a

lt

e

r

n

a

t

e

d

e

t

e

r

m

i

n

i

s

ti

c

n

o

n

e

8

b

i

t

3

2

b

it

6

4

b

it

d

c

c

r

c

/

e

x

t

e

r

n

a

l

i

n

t

e

r

n

a

l

c

p

u

d

m

a