KS152JB Universal Communications Controller

Technical Specifications

Kawasaki LSI USA, Inc. Page 22 of 120 Ver. 0.9 KS152JB2

There are two ways to terminate the Idle mode. One way is to reset the processor and the other is

by activation of any enabled interrupt. On receiving an interrupt, the processor will vector to the

interrupt service routine and will start execution from here. After completion of the service rou-

tine, following the execution of RETI, the execution will continue from the instruction following

the one which put the processor into the Idle mode.

The signal at the RST pin is used to clear the IDL bit. The RST pin has to be held low for at least

24 clock periods to generate an internal reset. The clearing of IDL bit is done synchronously, so

that the CPU will restart from the same state phase condition that it went into Idle. This ensures

smooth transition from Idle mode to normal operation. Now the reset logic takes 19 clock periods

to activate the internal reset from the time where RST was sampled low. For this time the proces-

sor will continue operations carrying on from the next instruction which put the processor in the

Idle mode. On-chip hardware prevents any writes to RAM during this period. but accesses to ports

is not inhibited. To prevent unexpected outputs at the port pins, the instruction after the one which

causes the Idle mode should not be an assess to the ports or External RAM.

The GSC continues to operate in Idle as long as the interrupts are enabled. The interrupts need to

be enabled, so that the CPU can service the FIFO’s. In order to properly terminate a reception or

transmission the C152 must not be in idle when the EOF is transmitted or received. After servic-

ing the GSC, user software will need to again invoke the Idle command as the CPU does not auto-

matically re-enter the Idle mode after servicing the interrupts.

The GSC does not operate while in Power Down so the steps required prior to entering Power

Down become more complicated. The sequence when entering Power Down and the status of the

I/O is of major importance in preventing damage to the C152 or other components in the system.

since the only way to exit Power Down is with a Reset, several problems that merit careful consid-

eration are cases where the Power Down occurs during the middle of a transmission, and the pos-

sibility that other stations are not or cannot enter this same mode. The state of the GSC I/O pins

becomes critical and the GSC status will need to be saved before power down is entered. There

will also need to be some method of identifying to the CPU that the following Reset is probably

not a cold start and that other stations on the link may have already been initialized.

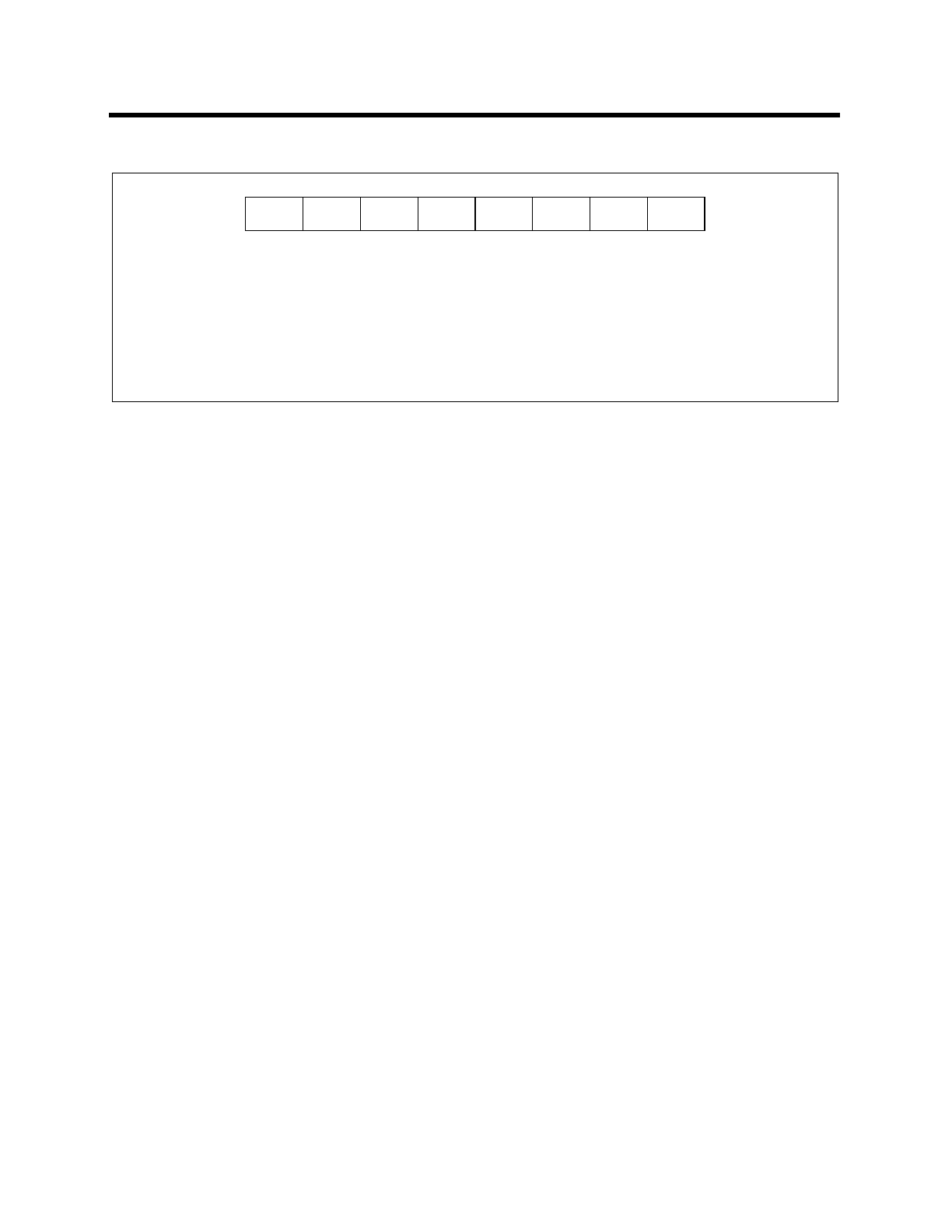

SMOD -- -- -- -- -- PD IDL

76543210

SMOD Double Baud Rate bit. When cleared, the baud rate is halved, by dividing the

PCON: Power Control Register.

serial clock by 2.

IDL Idle Mode bit. Setting this bit activates this mode.

PD Power Down bit. Setting this bit activates this mode.

-- Described later.