KS152JB Universal Communications Controller

Technical Specifications

Kawasaki LSI USA, Inc. Page 92 of 120 Ver. 0.9 KS152JB2

ARB enables the DMA logic to detect HLD and generate HLDA. After it has activated HLDA,

the C152 will not begin a new DMA to or from External Data Memory as long as

HLD is seen to

be active. This logic is disabled when ARB = 0, and enabled when ARB = 1.

REQ enables the DMA logic to generate HLD and detect HLDA before performing a DMA to or

from External Data Memory. After it has activated

HLD, the C152 will not begin the DMA until

HLDA is seen to be active. This logic is disabled when REQ = 0, and enabled when REQ = 1.

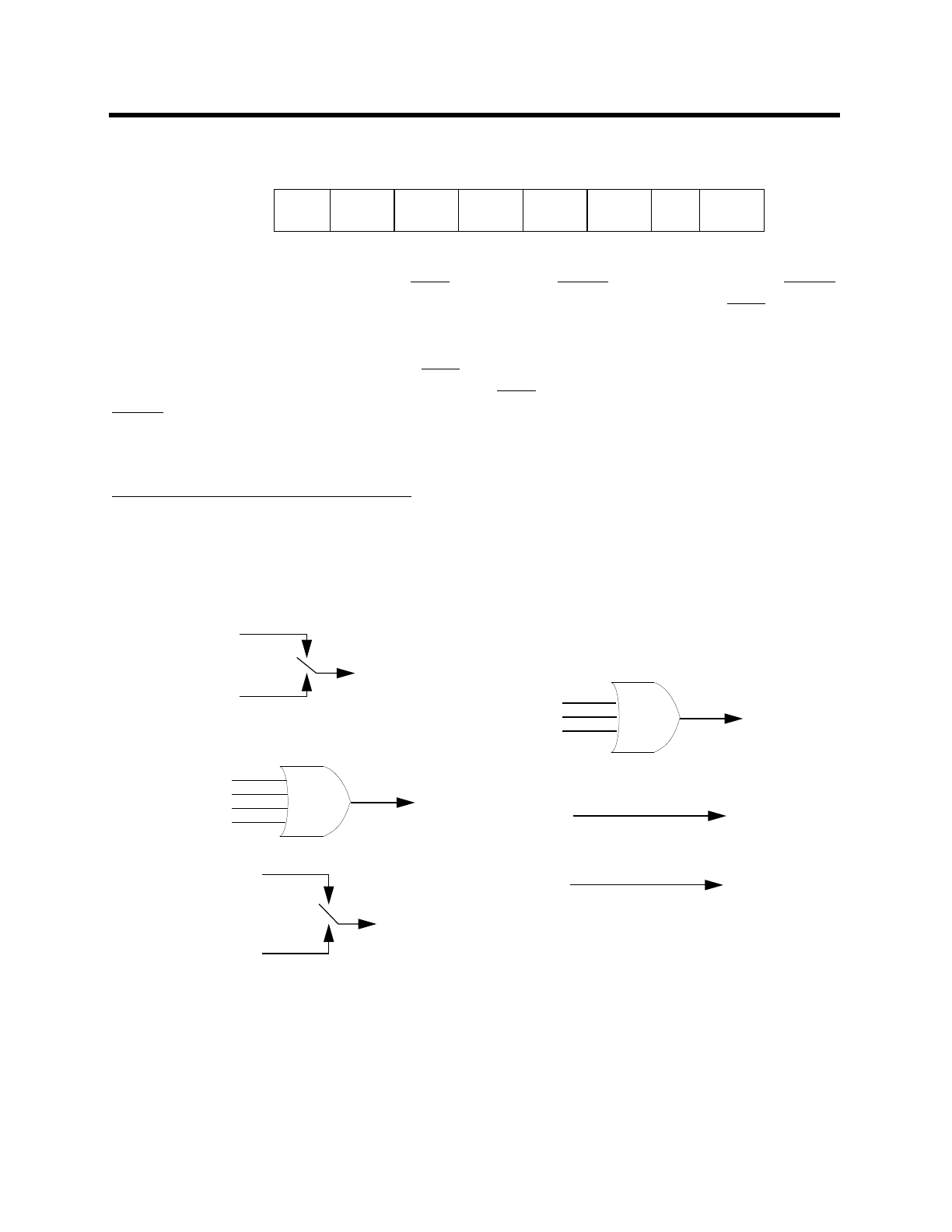

5.0 INTERRUPT STRUCTURE

The 8XC152 retains all five interrupts of the 80C51BH. Six new interrupts are added in the

8XC152, to support its GSC and DMA features. They are all listed below, and the flag that gener-

ate them are shown in Figure below.

GSCRV - GSC Receive Valid

GSCRE - GSC Receive Error

GSCTV - GSC Transmit Valid

GSCTE - GSC Transmit Error

DMA0 - DMA Channel0 Done

DMA1 - DMA Channel1 Done

SMOD ARB REQ GAREN XRCLK GFIEN PDN IDL

PCON

RFNE

RDN

DMA = 0

DMA = 1

GSCRV

CRCE

AE

RCABT

OVR

GSCRE

TFNF

TDN

GSCTV

TCDT

UR

NOACK

GSCTE

DONE

(DCON0.1)

DMA0

DONE

(DCON1.1)

DMA1

DMA = 0

DMA = 1