KS152JB Universal Communications Controller

Technical Specifications

Kawasaki LSI USA, Inc. Page 78 of 120 Ver. 0.9 KS152JB2

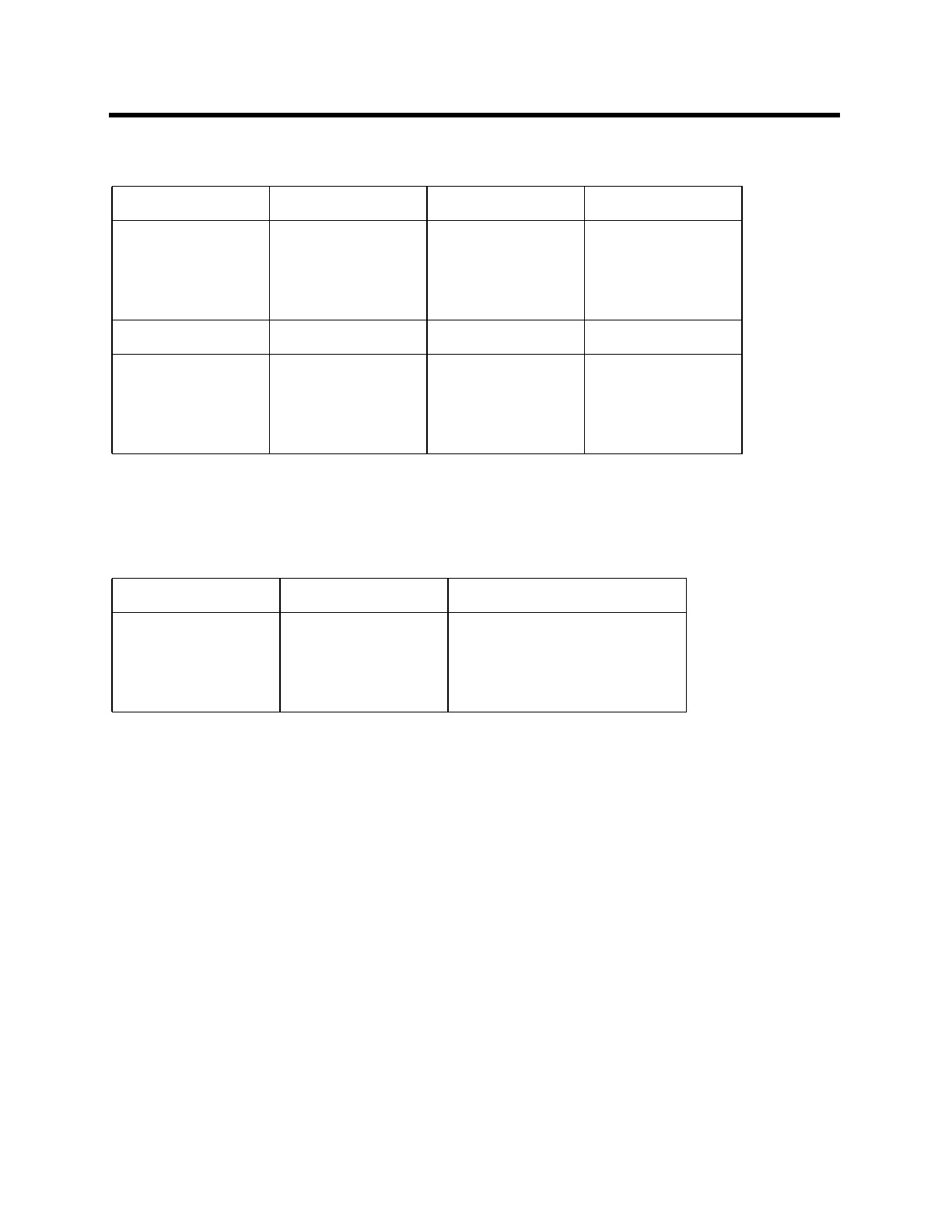

There are four modes in which the DMA channel can operate. These are selected by the bits DM

and TM (Demand Mode and Transfer Mode) in DCONn:

The operating modes are described below.

4.1.1 ALTERNATE CYCLE MODE

In Alternate Cycles Mode the DMA is initiated by setting the GO bit in DCONn. Following the

instruction that set the GO bit, one more instruction is executed, and then the first data byte is

transferred from the source address to the destination address. Then another instruction is exe-

cuted, and then another byte of data is transferred, and so on in this manner.

Each time a data byte is transferred, BCRn (Byte Count Register for DMA Channel n) is decre-

mented. When it reaches 0000H, on-chip hardware clears the GO bit and sets the DONE bit, and

the DMA ceases. The DONE bit flags an interrupt.

4.1.2 BURST MODE

Burst Mode differs from Alternate Cycles mode only in that once the data transfer has begun, pro-

gram execution is entirely suspended until BCRn reaches 0000H, indicating that all data bytes

that were to be transferred have been transferred. The interrupt control hardware remains active

DAS IDA Destination Auto-Increment

0

0

1

1

0

1

0

1

External RAM

External RAM

SFR

Internal RAM

no

yes

no

yes

SAS ISA Source Auto-Increment

0

0

1

1

0

1

0

1

External RAM

External RAM

SFR

Internal RAM

no

yes

no

yes

DM TM Operating Mode

0

0

1

1

0

1

0

1

Alternate Cycles Mode

Burst Mode

Serial Port Demand Mode

External Demand Mode