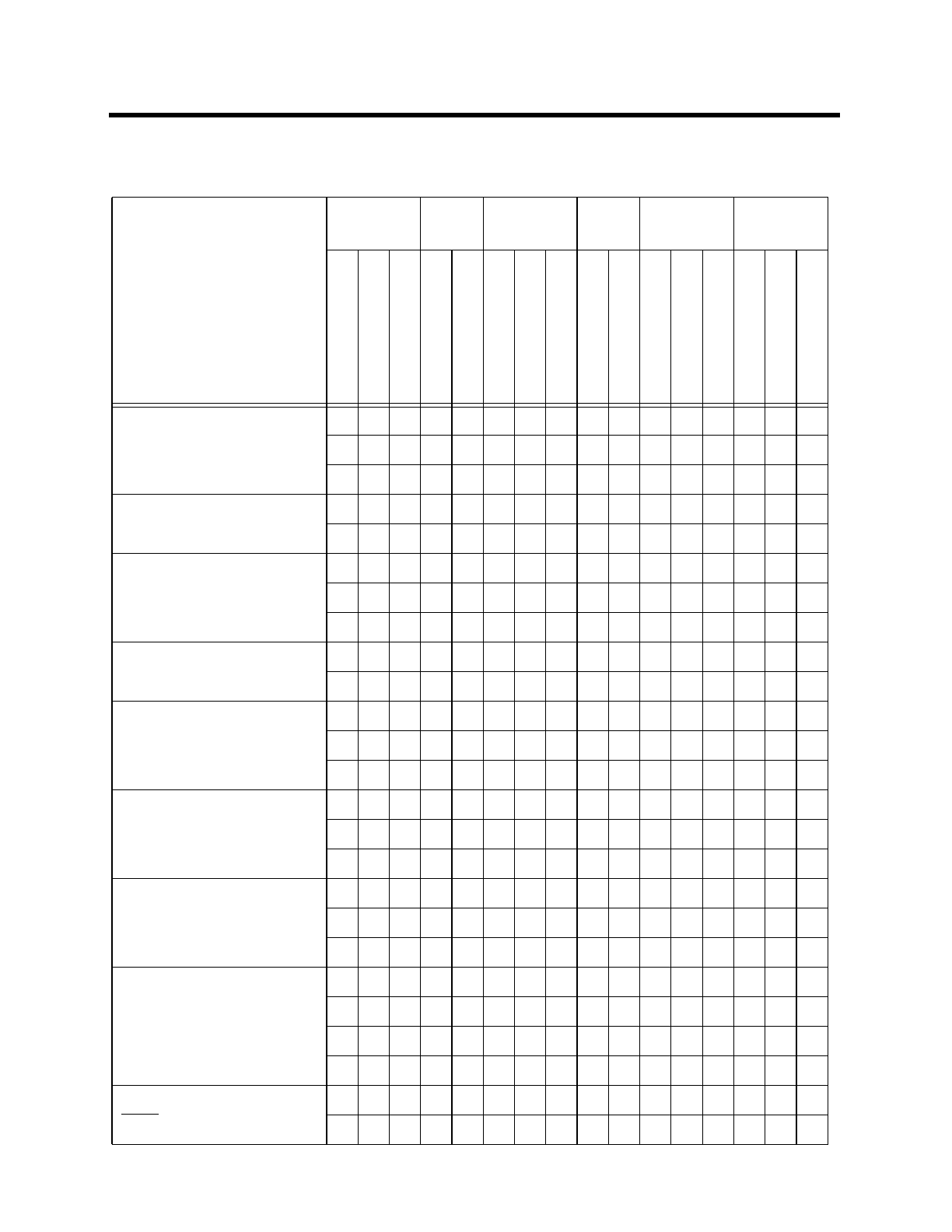

KS152JB Universal Communications Controller

Technical Specifications

Kawasaki LSI USA, Inc. Page 33 of 120 Ver. 0.9 KS152JB2

Table 9:

N-Not available.

M-Mandatory.

O-Optional.

P-Normally Preferred

X-N/A

Data Flags CRC Duplex Ack

Addr

recognition

m

a

n

c

h

ec

st

er

nr

z

nr

zi

0

1

1

1

1

1

1

0

1

1/

id

le

n

o

n

e

1

6-

bi

t

cc

it

3

2

bi

ta

ut

o

h

al

f

d

u

pl

e

x

fu

ll

d

u

pl

e

x

n

o

n

e

h

ar

d

w

ar

e

us

er

d

ef

n

o

n

e/

al

l

8

bi

t

1

6

bi

t

Manchester (csma/cd)

NRZI (sdlc)

NRZ (ext clock)

XNN1 P1 OOMNOOOOOO

NXNP1 1 OOOOONPOOO

NNXOO1 OOOOONOOOO

Flags:01111110(sdlc)

11/IDLE

NPOX1 1 OOOOONPOOO

PNO1 X1 OOONOOOOOO

CRC: NONE

16-bit CCITT

32-bitAUTODIN II

11111XNN1 N111111

OOOOONXNOOOOOOOO

OOOOONNXONOOOOOO

Half Duples

Full Duplex

OOOOO1 OOXNOOOOOO

NOOMNNMNNXONPOOO

Acknowledge: None

Hardware

User defined.

OOOOO1 OOOOXNNOOO

ONNNO1 OOONNXNOOO

OPOOO1 OOOPNNXOOO

Address recog: none

8-bit

16 bit

OOOOO1 OOOOOOOXNN

OOOOO1 OOOOOOONXN

OOOOO1 OOOOOOONNX

Coll resol: Normal

Alternate

Deterministic

ONONONOOMNONOOOO

ONONONOOMNOOOOOO

ONONONOOMNOOOOOO

Preamble: None

8-bit

32-bit

64-bit

NOOO1 1 OOOOONOOOO

OOOOO1 OOOOOOOOOO

OOOOO1 OOOOOOOOOO

OOOOO1 OOOOOOOOOO

DC JAM

CRC JAM

MNNNONOOMNOOOOOO

MNNNONOOMNOOOOOO