5-2 Netra CP3260 Blade Server User’s Guide • April 2009

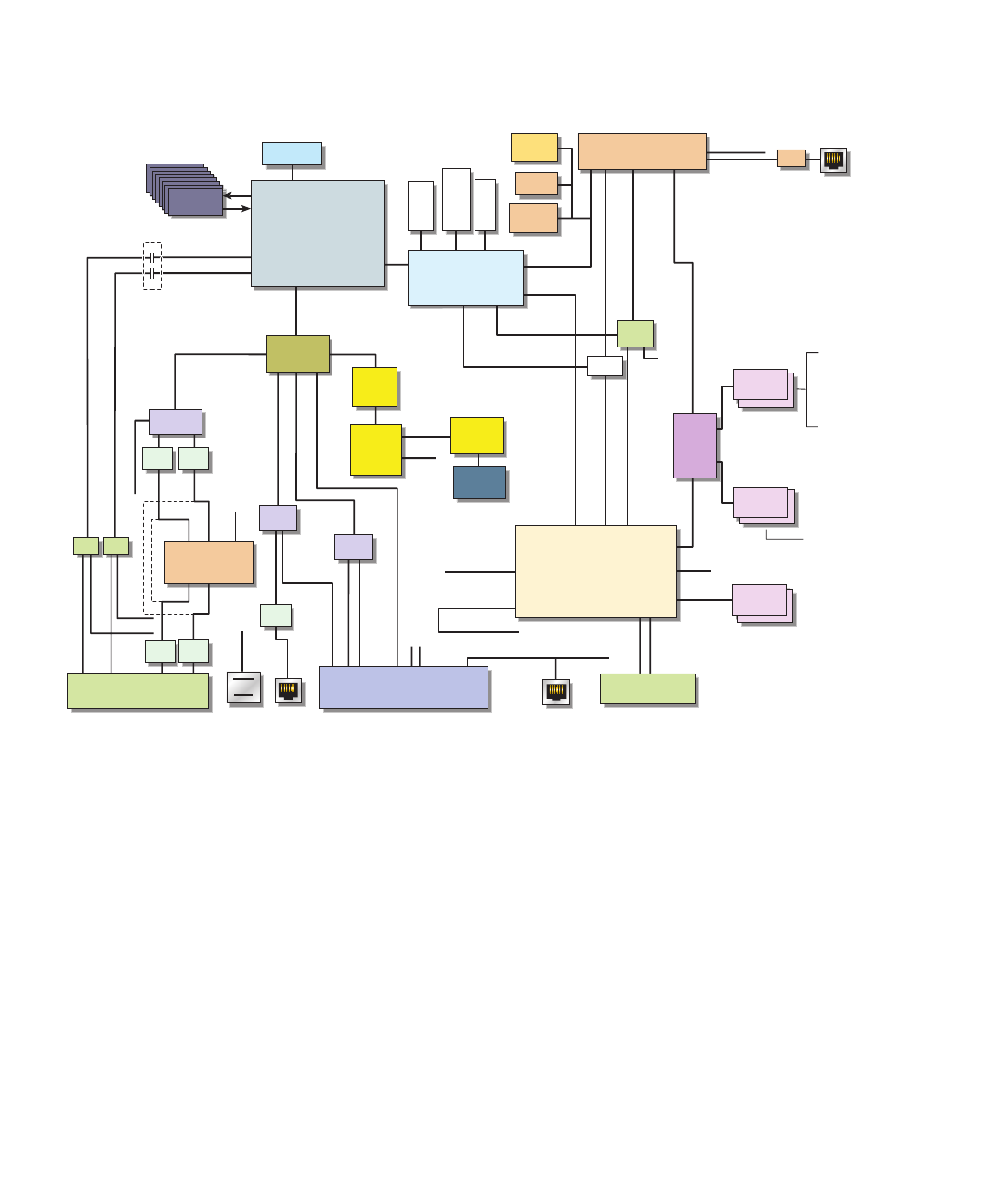

FIGURE 5-1 Netra CP3260 Blade Server Block Diagram

5.1.1 UltraSPARC T2 Processor and Memory

The UltraSPARC T2 processor has eight SPARC physical processor cores. Each

SPARC physical processor core has full hardware support for eight strands, two

integer execution pipelines, one floating-point execution pipeline, and one memory

pipeline. The eight SPARC cores are connected through a crossbar to an on-chip

unified 4-Mbyte, 16 way associative L2 cache.

NOTES:

1) Functions in orange are for Power PC

2) Functions in yellow are replacing Southbridge

UltraSPARC

T2

Processor

FBDIMM

BRANCH 0-3

X8 PCI

EXPRESS

I2C

XAUI

0 1

SSI

JTAG

FPGA

SSI

N2 JTAG

X4

X4 X4

X4

X8

X8

FBDIMM

I2C

HOST (OBP)

FLASH

FPGA

FLASH

TPM

RJ45

Serial

Dual

GBE

Dual

GBE

Dual

GBE

8 FBDIMM SLOTS

FRONT PANEL

ETHERNET

CF

Flash

I2C (Netconsole)

H8

Parallel Bus

Payload (RS232)

Serial RS232

MUX

Serial RS232

POWER PC

MPC885 66MHz

DOC

MD4832

PPC

FLASH

SP SDRAM

256 MB

PPC Ethernet

RMII

PPC

Ethernet

RMII

PPC Ethernet

RMII – Port 2

10/100/1000

MGMNT

PPC

Parallel Bus

Debug

FRONT/REAR

SERIAL

CONSOLE

I2C

Selector

PPC

I2C

ADM1026

IPMI FRUID

SEL EEPROM

DC-DC

Telco Daughter Card

I2C Devices

I2C Devices

I2C Devices

SMM15

FLASH_SEL

OBP/HV

SP NVRAM

SUNFRUID

SCC_MAC

FBDIMM SPD[0..7]

RTM

IPMC_I2C

SYS_I2C

Payload

0 Ohm

Console

I2C (Netconsole)

FRONT/REAR

SERIAL CONSOLE

Front board header

H8

Serial

I2C

I2C

I2C

I2C

Parallel Bus

I/F

Serial

Payload

Serial

Netconsole

SSI

D190 (Vcore)

PCI-E

SWITCH 0

Midplane Zone 1

IPMB

0 10 1

Base

Midplane Zone 2

Fabric

BCM5397

Switch

(5 port+RGMII/GMII)

PCIe-PCI

Bridge

USB 2,3

Zone 3 RTM

PCI-EXP

ETHERNET

(Mgmnt)

ETHERNET

ETHERNET

SERIAL

Console

XAUI

USB 2,3

5 port

USB Hub

TI

TUSB6250

USB-IDE

PHY

10/100

BASE-T

DC Blocking

caps.

PORT 0

PORT 1

PORT 10

PORT 9

PORT 2

PORT 8

MUX MUX

XFMR XFMR

XFMR XFMR

XFMR

XAUI_RTM

XAUI_RTM