www.ti.com

4.12.27VideoDisplayField1VerticalBlankingBitRegister(VDVBIT1)

VideoDisplayRegisters

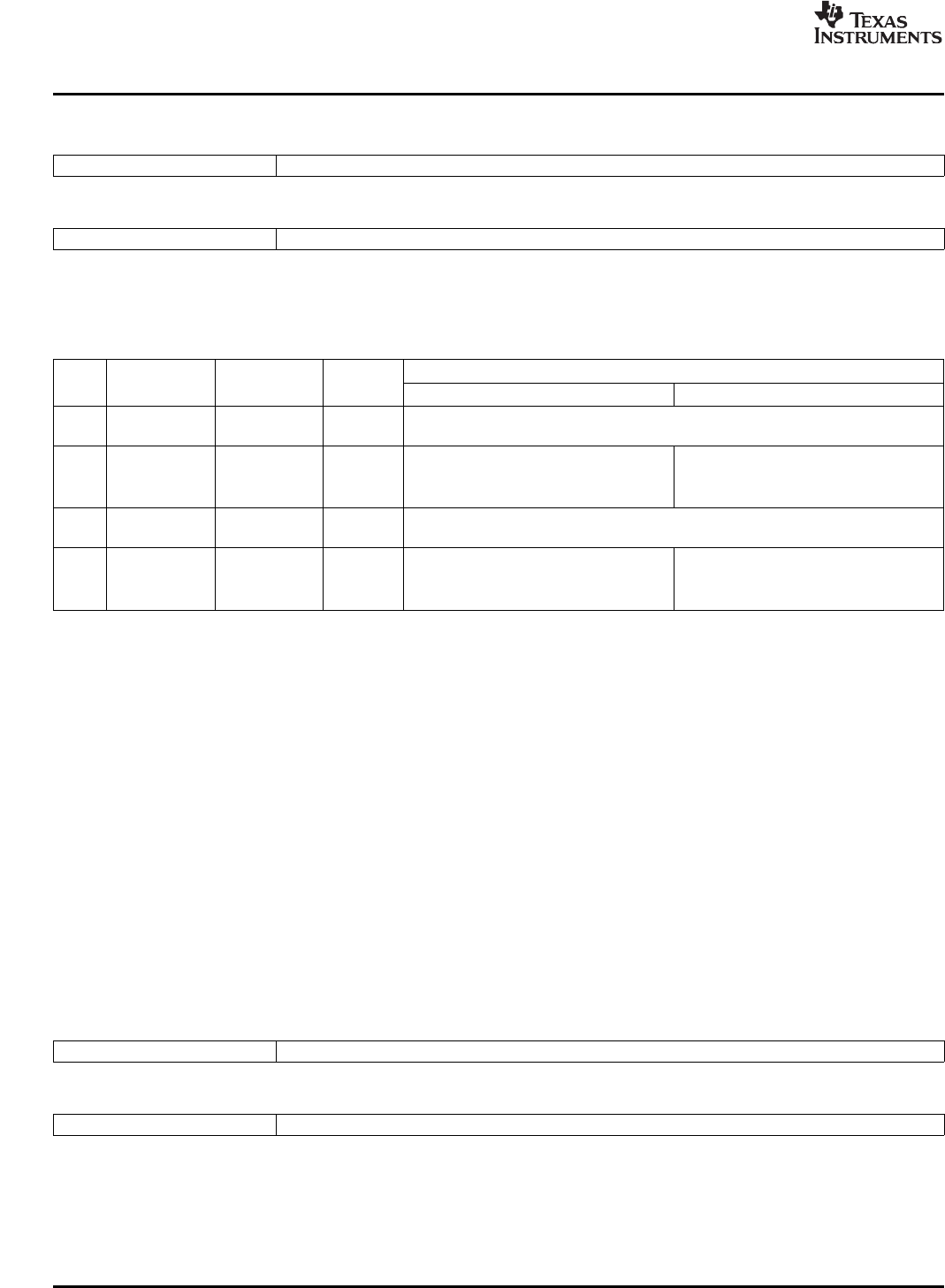

Figure4-57.VideoDisplayFieldBitRegister(VDFBIT)

31282716

ReservedFBITSET

R-0R/W-0

1512110

ReservedFBITCLR

R-0R/W-0

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table4-31.VideoDisplayFieldBitRegister(VDFBIT)FieldDescriptions

Description

Bitfield

(1)

symval

(1)

ValueBT.656andY/CModeRawDataMode

31-28Reserved-0Reserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfield

hasnoeffect.

27-16FBITSETOF(value)0-FFFhSpecifiesthefirstlinewithanEAVofF=Notused.

1indicatingfield2display.

DEFAULT0

15-12Reserved-0Reserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfield

hasnoeffect.

11-0FBITCLROF(value)0-FFFhSpecifiesthefirstlinewithanEAVofF=Notused.

0indicatingfield1display.

DEFAULT0

(1)

ForCSLimplementation,usethenotationVP_VDFBIT_field_symval

Thevideodisplayfield1verticalblankingbitregister(VDVBIT1)controlstheVbitvalueintheEAVand

SAVtimingcontrolcodesforfield1.

TheVBITSET1andVBITCLR1bitscontroltheVbitvalueintheEAVandSAVtimingcontrolcodes.The

Vbitissetto1(indicatingthestartoffield1digitalverticalblanking)intheEAVcodeatthebeginningof

thelinewhenevertheframelinecounter(FLCOUNT)isequaltoVBITSET1.Itremainsa1forall

EAV/SAVcodesuntiltheEAVatthebeginningofthelineonwhenFLCOUNT=VBITCLR1whereit

changesto0(indicatingthestartofthefield1digitalactivedisplay).TheVbitoperationiscompletely

independentoftheVBLNKcontrolsignal.

TheVBITSET1andVBITCLR1bitsshouldbeprogrammedsothatFLCOUNTbecomessetto1during

field1verticalblanking.Thehardwareonlystartsgeneratingfield1EDMAeventswhenFLCOUNT=1.

Thevideodisplayfield1verticalblankingbitregister(VDVBIT1)isshowninFigure4-58anddescribedin

Table4-32.

Figure4-58.VideoDisplayField1VerticalBlankingBitRegister(VDVBIT1)

31282716

ReservedVBITCLR1

R-0R/W-0

1512110

ReservedVBITSET1

R-0R/W-0

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

VideoDisplayPort 146SPRUEM1–May2007

SubmitDocumentationFeedback