www.ti.com

5.1.5VideoPortPinDataInputRegister(PDIN)

GPIORegisters

PDINreflectsthestateofthevideoportpins.Whenread,PDINreturnsthevaluefromthepin'sinput

buffer(withappropriatesynchronization)regardlessofthestateofthecorrespondingPFUNCorPDIRbit.

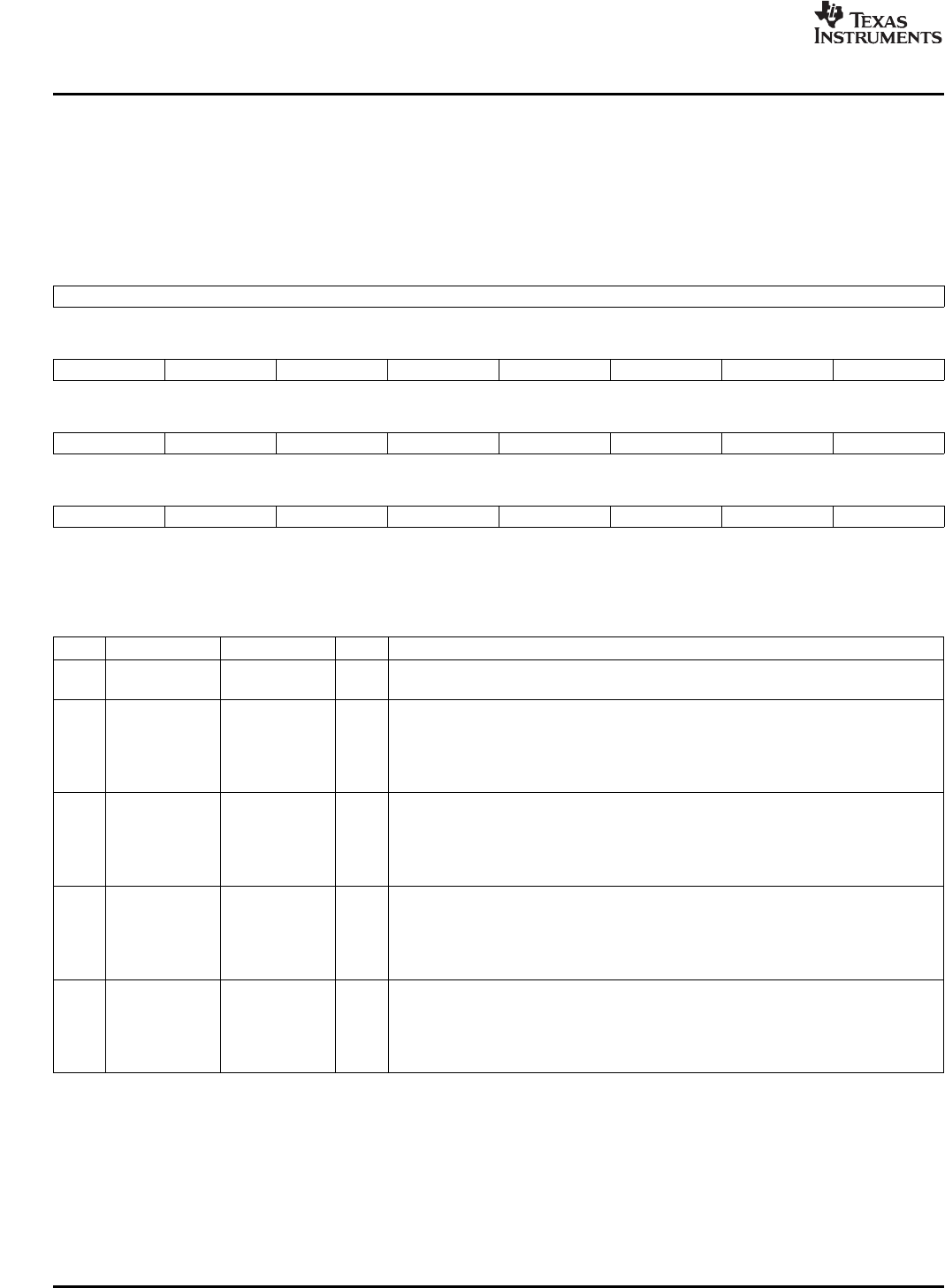

Theread-onlyvideoportpindatainputregister(PDIN)isshowninFigure5-5anddescribedinTable5-6.

Figure5-5.VideoPortPinDataInputRegister(PDIN)

3124

Reserved

R-0

2322212019181716

ReservedPDIN22PDIN21PDIN20PDIN19PDIN18PDIN17PDIN16

R-0R-0R-0R-0R-0R-0R-0R-0

15141312111098

PDIN15PDIN14PDIN13PDIN12ReservedReservedPDIN9PDIN8

R-0R-0R-0R-0R-0R-0R-0R-0

76543210

PDIN7PDIN6PDIN5PDIN4PDIN3PDIN2ReservedReserved

R-0R-0R-0R-0R-0R-0R-0R-0

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table5-6.VideoPortPinDataInputRegister(PDIN)FieldDescriptions

Bitfield

(1)

symval

(1)

ValueDescription

31-23Reserved-0Reserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfield

hasnoeffect.

22PDIN22OF(value)PDIN22bitreturnsthelogicleveloftheVCTL3pin.

DEFAULT0Pinislogiclow.

VCTL3LO

VCTL3HI1Pinislogichigh.

21PDIN21OF(value)PDIN21bitreturnsthelogicleveloftheVCTL2pin.

DEFAULT0Pinislogiclow.

VCTL2LO

VCTL2HI1Pinislogichigh.

20PDIN20OF(value)PDIN20bitreturnsthelogicleveloftheVCTL1pin.

DEFAULT0Pinislogiclow.

VCTL1LO

VCTL1HI1Pinislogichigh.

19-2PDIN[19-2]OF(value)PDIN[19-2]bitreturnsthelogiclevelofthecorrespondingVDATA[n]pin.

DEFAULT0Pinnislogiclow.

VDATAnLO

VDATAnHI1Pinnislogichigh.

(1)

ForCSLimplementation,usethenotationVP_PDIN_PDINn_symval

General-PurposeI/OOperation 158SPRUEM1–May2007

SubmitDocumentationFeedback