www.ti.com

6.5.3VICClockDividerRegister(VICDIV)

Divider + Round

ƪ

DCLK

ń

R

]

VICPortRegisters

TheVICclockdividerregister(VICDIV)definestheclockdividerfortheVICinterpolationfrequency.The

VICinterpolationfrequencyisobtainedbydividingthemoduleclock.ThedividervaluewrittentoVICDIV

is:

whereDCLKistheCPUclockdividedby2,andRisthedesiredinterpolationfrequency.Theinterpolation

frequencydependsonprecisionβ.

ThedefaultvalueofVICDIVis0001h;0000hisanillegalvalue.TheVICmoduleusesavalueof0001h

whenever0000hiswrittentothisregister.

TheDSPcanwritetoVICDIVonlywhentheGObitinVICCTLisclearedto0.Ifawriteisperformedwhen

theGObitissetto1,theVICDIVbitsremainunchanged.

TheVICclockdividerregister(VICDIV)isshowninFigure6-5anddescribedinTable6-6.

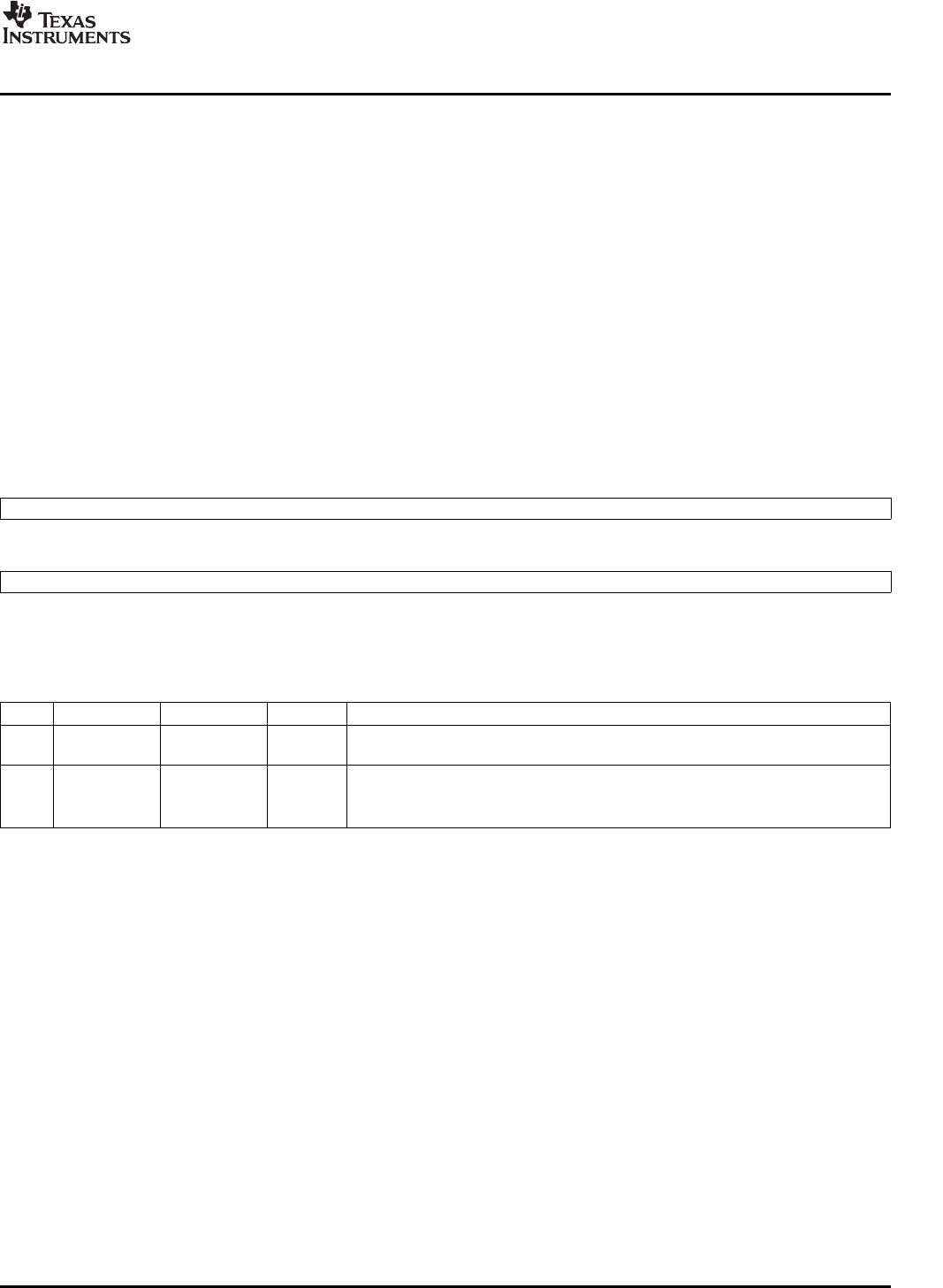

Figure6-5.VICClockDividerRegister(VICDIV)

3116

Reserved

R-0

150

VICCLKDIV

R/W-0001h

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table6-6.VICClockDividerRegister(VICDIV)FieldDescriptions

Bitfieldsymval

(1)

ValueDescription

31-16Reserved-0Reserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfield

hasnoeffect.

15-0VICCLKDIVOF(value)0-FFFFhTheVICclockdividerbitsdefinetheclockdividerfortheVICinterpolation

frequency.

DEFAULT1h

(1)

ForCSLimplementation,usethenotationVIC_VICDIV_VICCLKDIV_symval

SPRUEM1–May2007VCXOInterpolatedControlPort173

SubmitDocumentationFeedback