www.ti.com

2.4.4VideoPortInterruptStatusRegister(VPIS)

VideoPortControlRegisters

Table2-5.VideoPortInterruptEnableRegister(VPIE)FieldDescriptions(continued)

Bitfield

(1)

symval

(1)

ValueDescription

3SERRAOF(value)ChannelAsynchronizationerrorinterruptenablebit.

DEFAULT0Interruptisdisabled.

DISABLE

ENABLE1Interruptisenabled.

2CCMPAOF(value)CapturecompleteonchannelAinterruptenablebit.

DEFAULT0Interruptisdisabled.

DISABLE

ENABLE1Interruptisenabled.

1COVRAOF(value)CaptureoverrunonchannelAinterruptenablebit.

DEFAULT0Interruptisdisabled.

DISABLE

ENABLE1Interruptisenabled.

0VIEOF(value)Videoportglobalinterruptenablebit.MustbesetforinterrupttobesenttoDSP.

DEFAULT0Interruptisdisabled.

DISABLE

ENABLE1Interruptisenabled.

Thevideoportinterruptstatusregister(VPIS)displaysthestatusofvideoportinterruptstotheDSP.The

interruptisonlysenttotheDSPifthecorrespondingenablebitinVPIEisset.AllVPISbitsareclearedby

writinga1,writinga0hasnoeffect.

Thevideoportinterruptstatusregister(VPIS)isshowninFigure2-4anddescribedinTable2-6.

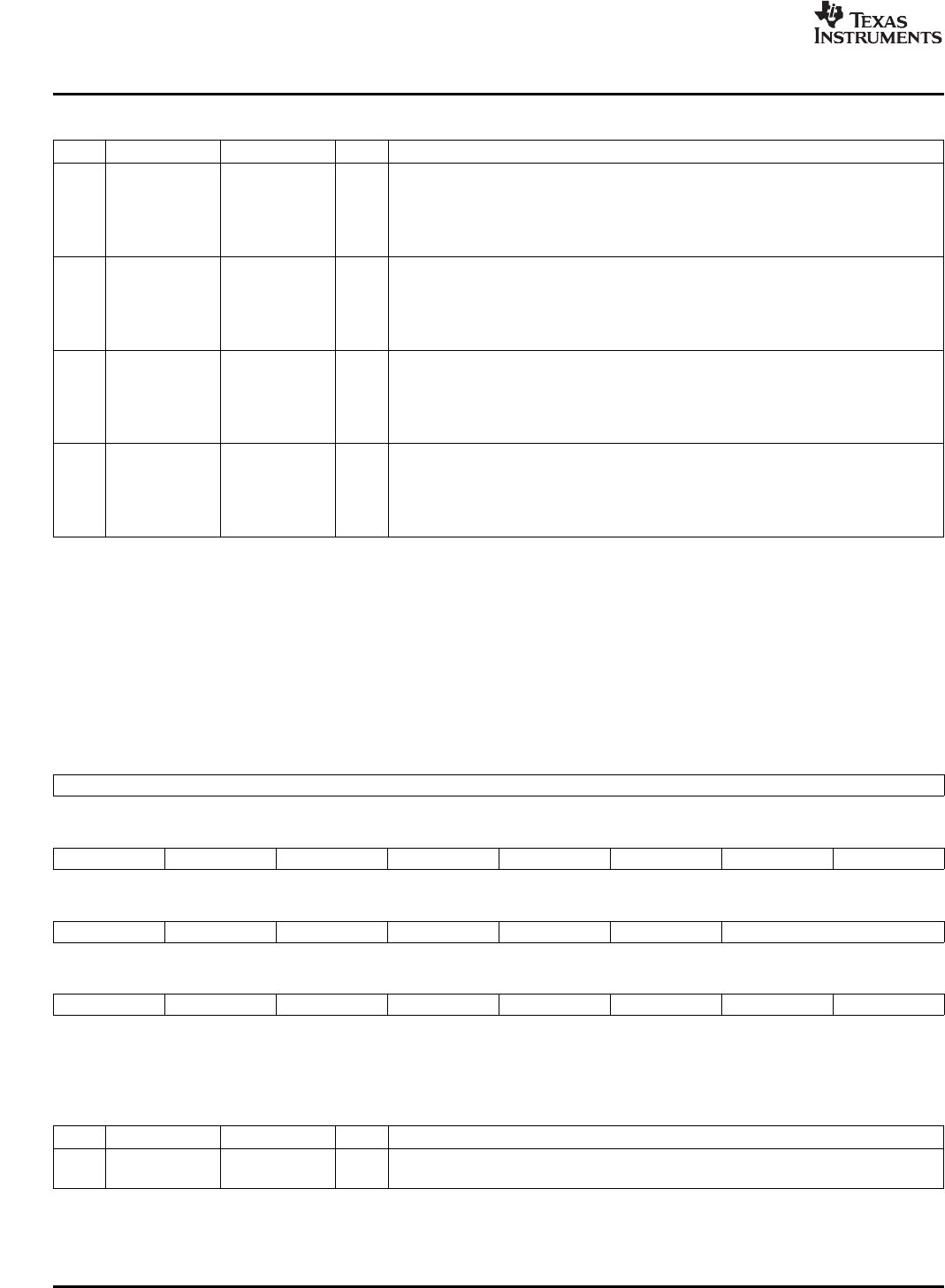

Figure2-4.VideoPortInterruptStatusRegister(VPIS)

3124

Reserved

R-0

2322212019181716

LFDBSFDBVINTB2VINTB1SERRBCCMPBCOVRBGPIO

R/WC-0R/WC-0R/WC-0R/WC-0R/WC-0R/WC-0R/WC-0R/WC-0

15141312111098

ReservedDCNADCMPDUNDTICKSTCReserved

R-0R/WC-0R/WC-0R/WC-0R/WC-0R/WC-0R-0

76543210

LFDASFDAVINTA2VINTA1SERRACCMPACOVRAReserved

R/WC-0R/WC-0R/WC-0R/WC-0R/WC-0R/WC-0R/WC-0R-0

LEGEND:R=Readonly;WC=Write1toclear,awriteof0hasnoeffect;-n=valueafterreset

Table2-6.VideoPortInterruptStatusRegister(VPIS)FieldDescriptions

Bitfield

(1)

symval

(1)

ValueDescription

31-24Reserved-0Reserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfield

hasnoeffect.

(1)

ForCSLimplementation,usethenotationVP_VPIS_field_symval

40VideoPortSPRUEM1–May2007

SubmitDocumentationFeedback