www.ti.com

27 MHz

Modulo 300

Counter 233

PCR Extension

PCR Base

CTMODE

0

1

STCLK

90 kHz

External VCXO

3.8.5TCIDataCaptureNotification

TCICaptureMode

countercountsfrom0to299at27MHz.Eachtimethe9-bitcounterrollsoverto0,the33-bitcounteris

incrementedby1.ThisisequivalenttothePCRtimestamptransmittedinthebit-stream.The33-bitfield

canalsobeprogrammedtocountat27MHzforcompatibilitywiththeMPEG-132-bitPCR,bysettingthe

CTMODEbitinVCCTLto1;inwhichcase,thePCRextensionportionofthecounterisnotused.

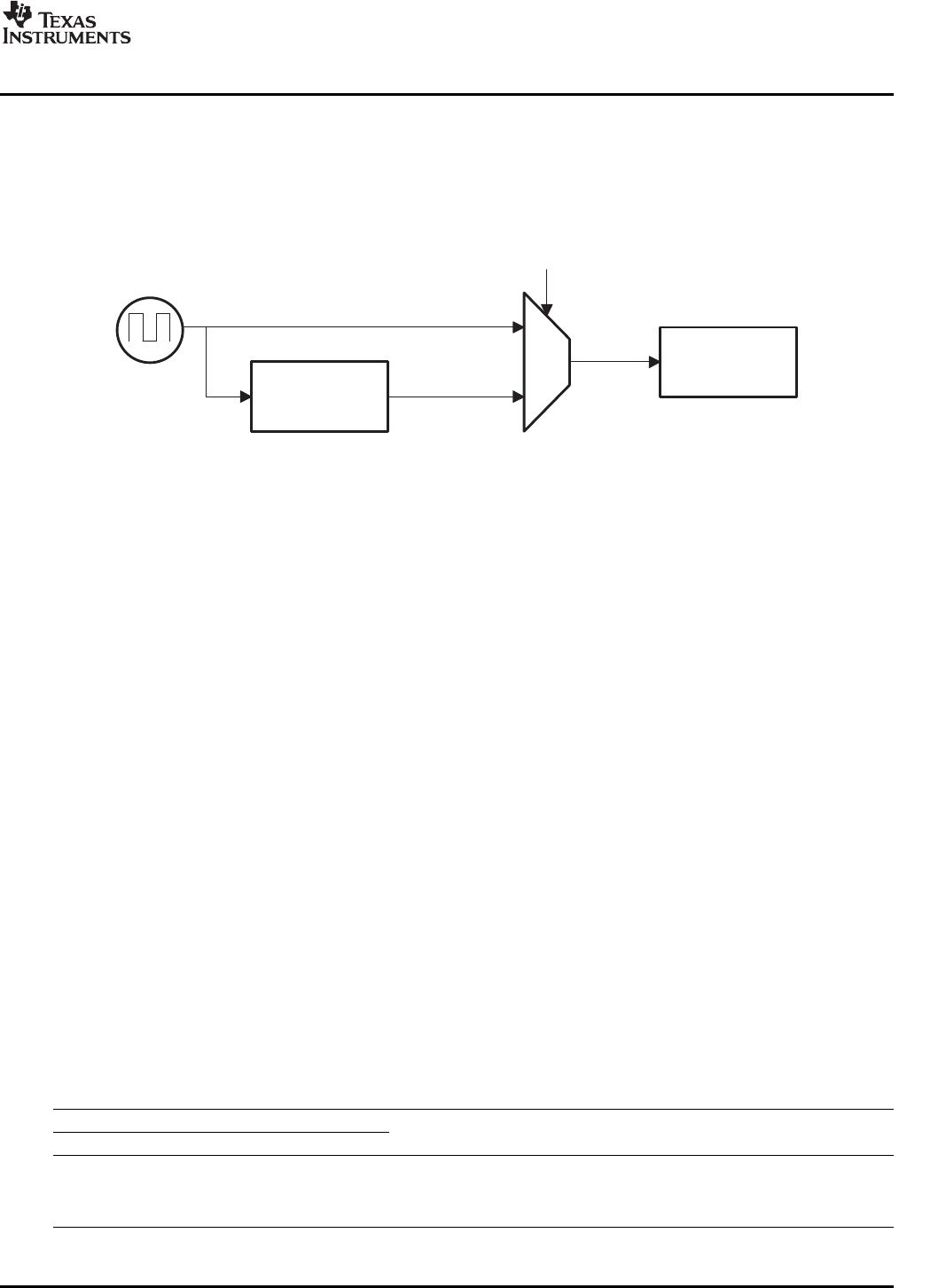

Figure3-17showsthesystemtimeclockcounteroperation.

Figure3-17.SystemTimeClockCounterOperation

Onreceptionofapacket(duringthesyncbyte),asnapshotofthecounteriscaptured.Thissnapshot,or

timestamp,isinsertedinthereceivingFIFOattheendofeachdatapacket.Softwareusesthistimestamp,

todeterminethedeviationofthelocalsystemtimeclockfromtheencodertimeclock.Anytimeapacket

withaPCRheaderisreceived,thetimestampforthatpacketiscomparedwiththePCRvalueby

software.APLLisimplementedinsoftwaretosynchronizetheSTCLKwiththeencodertimeclockvalue

inthePCR.ThisalgorithmthendrivestheVIC,whichdrivestheVDACoutputtotheexternalVCXO,

whichsuppliesSTCLK.

ThesystemtimeclockcounterisinitializedbysoftwarewiththePCRofthefirstpacketwithaPCR

header.Afterinitialization,thecountercanbereinitializedbysoftwareupondetectingadiscontinuityin

subsequentpacketPCRheadervalues.

ThesystemtimeismadeavailabletotheDSPatanytimethroughthesystemtimeclockregisters

(TCISTCLKLandTCISTCLKM).TheDSPcanprogramthevideoporttointerrupttheDSPwhenevera

specificsystemtimeisreachedorwheneveraspecificnumberofsystemtimeclockcycleshaveelapsed.

SinceTCImodecapturesonlydatapackets,thereisnoneedforfieldcontrol.Someflexibilityincapture

andDSPnotificationisstillprovidedinordertoaccommodatevariousEDMAstructuresandprocessing

flows.EachTCIdatapacketistreatedsimilartoaprogressivescanvideoframe.TheTCImodeusesthe

CONandFRAMEbitsofVCACTLinaslightlydifferentmanner,aslistedinTable3-12.

TheCONbitcontrolsthecaptureofmultiplepackets.WhenCON=1,continuouscaptureisenabled,the

videoportcapturesincomingdatapackets(assumingtheVCENbitisset)withouttheneedforDSP

interaction.ItreliesonaEDMAstructurewithcircularbufferingcapabilitytoservicethecaptureFIFO.

WhenCON=0,continuouscaptureisdisabled,thevideoportsetstheframecapturecompletebit

(FRMC)inVCASTATuponthecaptureofeachpacket.Oncethecapturecompletebitisset,atmost,one

moreframecanbereceivedbeforecaptureoperationishalted(asdeterminedbytheFRAMEbitstate).

ThispreventssubsequentdatafromoverwritingpreviouspacketsuntiltheDSPhasachancetoupdate

EDMApointersorprocessthosepackets.

Table3-12.TCICaptureModeOperation

VCACTLBit

CONFRAMECF2CF1Operation

00xxNoncontinuouspacketcapture.FRMCissetafterpacketcaptureandcauses

CCMPAtobeset.Capturewillhaltuponcompletionofthenextdatapacket

unlesstheFRMCbitiscleared.(DSPhastheentirenextdatapackettimeto

clearFRMC.)

SPRUEM1–May2007VideoCapturePort65

SubmitDocumentationFeedback