Signal Descriptions

148 Intel® Xeon® Processor E5-1600/E5-2600/E5-4600 Product Families

Datasheet Volume One

6.8 Serial VID Interface (SVID) Signals

6.9 Processor Asynchronous Sideband and

Miscellaneous Signals

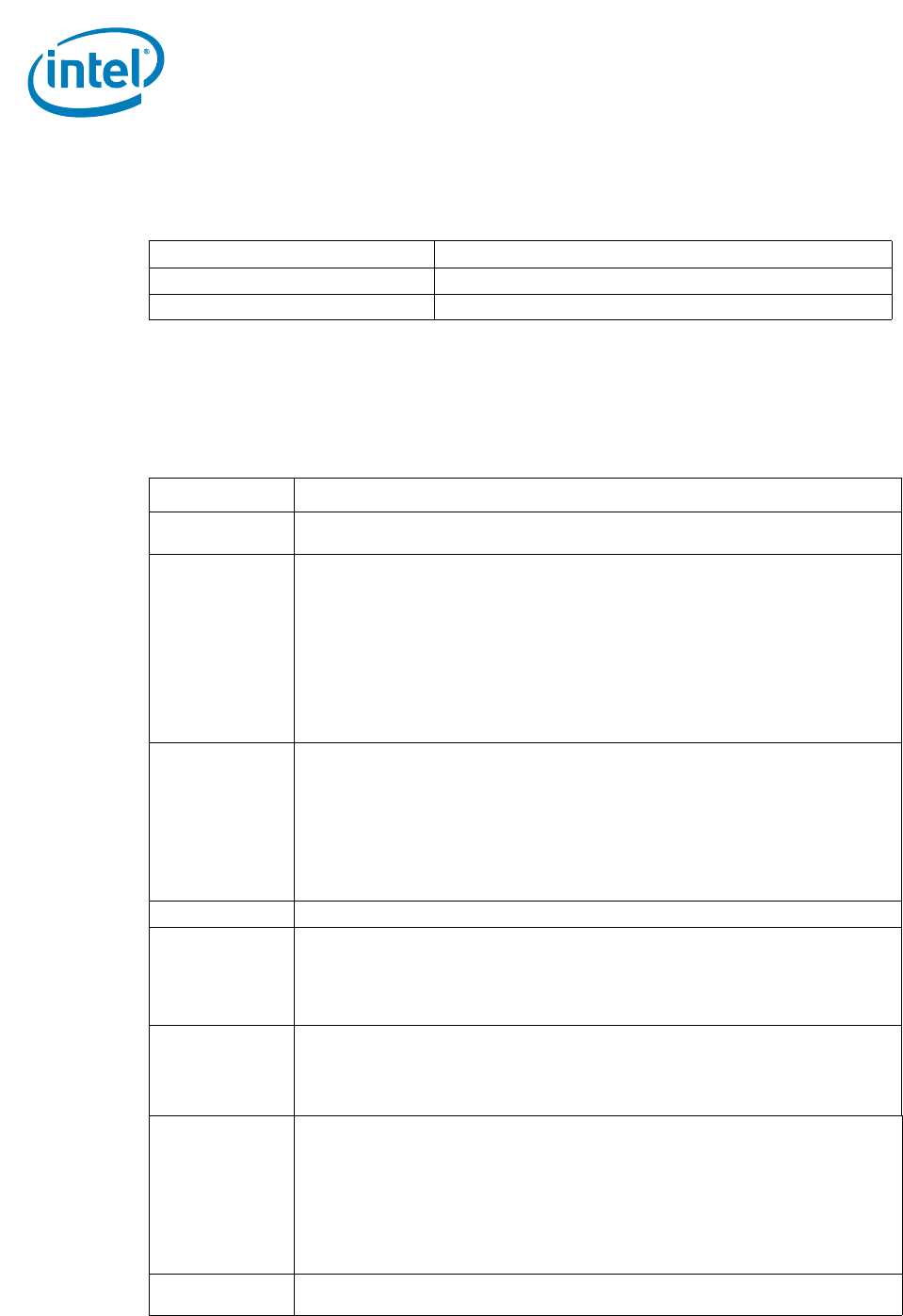

Table 6-13. SVID Signals

SVIDALERT_N Serial VID alert.

SVIDCLK Serial VID clock.

SVIDDATA Serial VID data out.

Table 6-14. Processor Asynchronous Sideband Signals (Sheet 1 of 3)

Signal Name Description

BIST_ENABLE BIST Enable Strap. Input which allows the platform to enable or disable built-in self test

(BIST) on the processor. This signal is pulled up on the die, refer to Table 7-6 for details.

BMCINIT BMC Initialization Strap. Indicates whether Service Processor Boot Mode should be used.

Used in combination with FRMAGENT and SOCKET_ID inputs.

• 0: Service Processor Boot Mode Disabled. Example boot modes: Local PCH (this

processor hosts a legacy PCH with firmware behind it), Intel QPI Link Boot (for

processors one hop away from the FW agent), or Intel QPI Link Init (for processors

more than one hop away from the firmware agent).

• 1: Service Processor Boot Mode Enabled. In this mode of operation, the processor

performs the absolute minimum internal configuration and then waits for the Service

Processor to complete its initialization. The socket boots after receiving a “GO”

handshake signal via a firmware scratchpad register.

This signal is pulled down on the die, refer to Table 7-6 for details.

CAT_ERR_N Indicates that the system has experienced a fatal or catastrophic error and cannot

continue to operate. The processor will assert CAT_ERR_N for nonrecoverable machine

check errors and other internal unrecoverable errors. It is expected that every processor

in the system will wire-OR CAT_ERR_N for all processors. Since this is an I/O land,

external agents are allowed to assert this land which will cause the processor to take a

machine check exception. This signal is sampled after PWRGOOD assertion.

On the processor, CAT_ERR_N is used for signaling the following types of errors:

• Legacy MCERR’s, CAT_ERR_N is asserted for 16 BCLKs.

• Legacy IERR’s, CAT_ERR_N remains asserted until warm or cold reset.

CPU_ONLY_RESET Resets all the processors on the platform without resetting the DMI2 links.

ERROR_N[2:0] Error status signals for integrated I/O (IIO) unit:

• 0 = Hardware correctable error (no operating system or firmware action necessary)

• 1 = Non-fatal error (operating system or firmware action required to contain and

recover)

• 2 = Fatal error (system reset likely required to recover)

FRMAGENT Bootable Firmware Agent Strap. This input configuration strap used in combination with

SOCKET_ID to determine whether the socket is a legacy socket, bootable firmware agent

is present, and DMI links are used in PCIe* mode (instead of DMI2 mode).

The firmware flash ROM is located behind the local PCH attached to the processor via the

DMI2 interface.This signal is pulled down on the die, refer to Table 7-6 for details.

MEM_HOT_C01_N

MEM_HOT_C23_N

Memory throttle control. MEM_HOT_C01_N and MEM_HOT_C23_N signals have two

modes of operation – input and output mode.

Input mode is externally asserted and is used to detect external events such as VR_HOT#

from the memory voltage regulator and causes the processor to throttle the appropriate

memory channels.

Output mode is asserted by the processor known as level mode. In level mode, the

output indicates that a particular branch of memory subsystem is hot.

MEM_HOT_C01_N is used for memory channels 0 & 1 while MEM_HOT_C23_N is used for

memory channels 2 & 3.

PMSYNC Power Management Sync. A sideband signal to communicate power management status

from the Platform Controller Hub (PCH) to the processor.