Power Management

88 Intel® Xeon® Processor E5-1600/E5-2600/E5-4600 Product Families

Datasheet Volume One

Notes:

1. Package C7 is not supported.

2. All package states are defined to be "E" states - such that they always exit back into the LFM point upon

execution resume

3. The mapping of actions for PC3, and PC6 are suggestions - microcode will dynamically determine which

actions should be taken based on the desired exit latency parameters.

4. CC3/CC6 will all use a voltage below the VccMin operational point; The exact voltage selected will be a

function of the snoop and interrupt response time requirements made by the devices (PCIe* and DMI) and

the operating system.

4.1.3 Integrated Memory Controller States

PC3 - Light

Retention

at least

one Core

in C3

•Core C-state

• Snoop Response Time

• Interrupt Response Time

• Non Snoop Response Time

Vcc = retention

PLL = OFF

No 2,3,4

PC6 - Deeper

Retention

CC6-CC7

•LLC ways open

• Snoop Response Time

• Non Snoop Response Time

• Interrupt Response Time

Vcc = retention

PLL = OFF

No 2,3,4

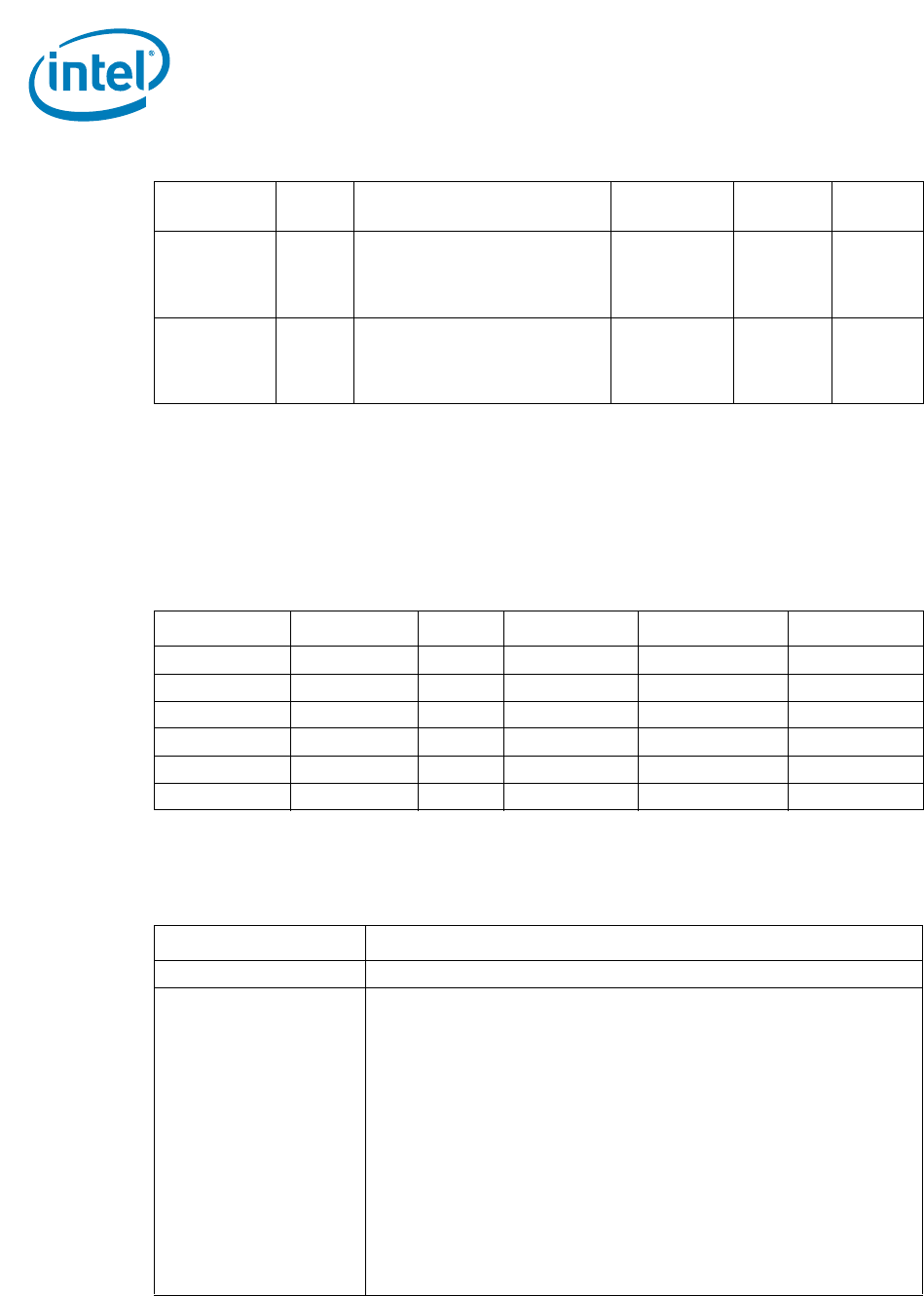

Table 4-2. Package C-State Support (Sheet 2 of 2)

Package C-

State

Core

States

Limiting Factors

Retention and

PLL-Off

LLC Fully

Flushed

Notes

1

Table 4-3. Core C-State Support

Core C-State Global Clock PLL L1/L2 Cache Core VCC Context

CC0 Running On Coherent Active Maintained

CC1 Stopped On Coherent Active Maintained

CC1E Stopped On Coherent Request LFM Maintained

CC3 Stopped On Flushed to LLC Request Retention Maintained

CC6 Stopped Off Flushed to LLC Power Gate Flushed to LLC

CC7 Stopped Off Flushed to LLC Power Gate Flushed to LLC

Table 4-4. System Memory Power States (Sheet 1 of 2)

State Description

Power Up/Normal Operation CKE asserted. Active Mode, highest power consumption.

CKE Power Down Opportunistic, per rank control after idle time:

• Active Power Down (APD) (default mode)

— CKE de-asserted. Power savings in this mode, relative to active idle

state is about 55% of the memory power. Exiting this mode takes 3

– 5 DCLK cycles.

• Pre-charge Power Down Fast Exit (PPDF)

— CKE de-asserted. DLL-On. Also known as Fast CKE. Power savings in

this mode, relative to active idle state is about 60% of the memory

power. Exiting this mode takes 3 – 5 DCLK cycles.

• Pre-charge Power Down Slow Exit (PPDS)

— CKE de-asserted. DLL-Off. Also known as Slow CKE. Power savings in

this mode, relative to active idle state is about 87% of the memory

power. Exiting this mode takes 3 – 5 DCLK cycles until the first

command is allowed and 16 cycles until first data is allowed.

• Register CKE Power Down:

— IBT-ON mode: Both CKE’s are de-asserted, the Input Buffer

Terminators (IBTs) are left “on”.

— IBT-OFF mode: Both CKE’s are de-asserted, the Input Buffer

Terminators (IBTs) are turned “off”.