Intel® Xeon® Processor E5-1600/E5-2600/E5-4600 Product Families 165

Datasheet Volume One

Electrical Specifications

7.4 Fault Resilient Booting (FRB)

The processor supports both socket and core level Fault Resilient Booting (FRB), which

provides the ability to boot the system as long as there is one processor functional in

the system. One limitation to socket level FRB is that the system cannot boot if the

legacy socket that connects to an active PCH becomes unavailable since this is the path

to the system BIOS. See Table 7-8 for a list of output tri-state FRB signals.

Socket level FRB will tri-state processor outputs via the PROCHOT_N signal. Assertion

of the PROCHOT_N signal through RESET_N de-assertion will tri-state processor

outputs. Note, that individual core disabling is also supported for those cases where

disabling the entire package is not desired.

The processor extends the FRB capability to the core granularity by maintaining a

register in the uncore so that BIOS or another entity can disable one or more specific

processor cores.

7.5 Mixing Processors

Intel supports and validates and four two processor configurations only in which all

processors operate with the same Intel QuickPath Interconnect frequency, core

frequency, power segment, and have the same internal cache sizes. Mixing

components operating at different internal clock frequencies is not supported and will

not be validated by Intel. Combining processors from different power segments is also

not supported.

Note: Processors within a system must operate at the same frequency per bits [15:8] of the

FLEX_RATIO MSR (Address: 194h); however this does not apply to frequency

transitions initiated due to thermal events, Extended HALT, Enhanced Intel SpeedStep

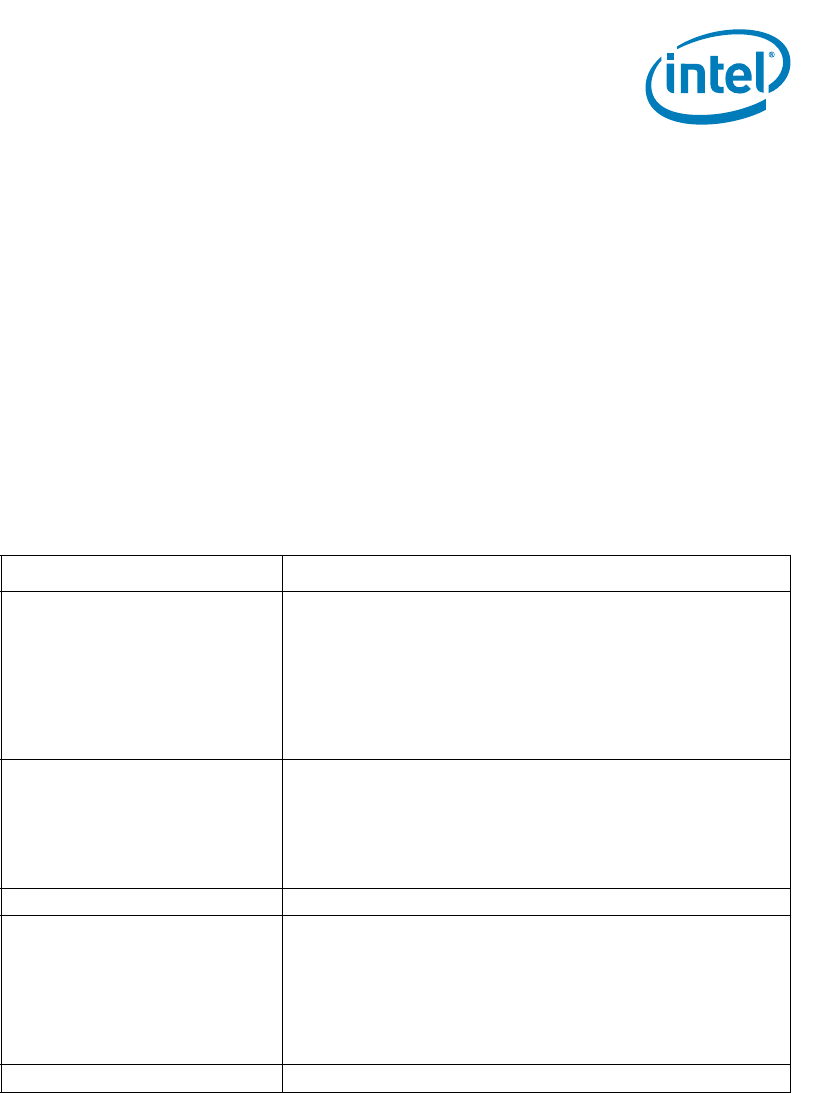

Table 7-8. Fault Resilient Booting (Output Tri-State) Signals

Output Tri-State Signal Groups Signals

Intel QPI

QPI0_CLKTX_DN[1:0]

QPI0_CLKTX_DP[1:0]

QPI0_DTX_DN[19:00]

QPI0_DTX_DP[19:00]

QPI1_CLKTX_DN[1:0]

QPI1_CLKTX_DP[1:0]

QPI1_DTX_DN[19:00]

QPI1_DTX_DP[19:00]

SMBus

DDR_SCL_C01

DDR_SDA_C01

DDR_SCL_C23

DDR_SDA_C23

PEHPSCL

PEHPSDA

JTAG & TAP TDO

Processor Sideband

CAT_ERR_N

ERROR_N[2:0]

BPM_N[7:0]

PRDY_N

THERMTRIP_N

PROCHOT_N

PECI

SVID SVIDCLK