Intel® Xeon® Processor E5-1600/E5-2600/E5-4600 Product Families 179

Datasheet Volume One

Note:

1. These signals are measured between VIL and VIH.

2. The signal edge rate must be met or the signal must transition monotonically to the asserted state.

V

IH

Input High Voltage 0.7*VTT V

V

OL

Output Low Voltage 0.2*V

TT

V

V

OH

Output High Voltage V

TT(max)

V

R

ON

Buffer On Resistance 14 Ω

I

L

Leakage Current

Signals DDR_SCL_C{01/23}, DDR_SDA_C{01/

23}

-100 +100 μA

I

L

Leakage Current

Signals PEHPSCL, PEHPSDA

+900 μA

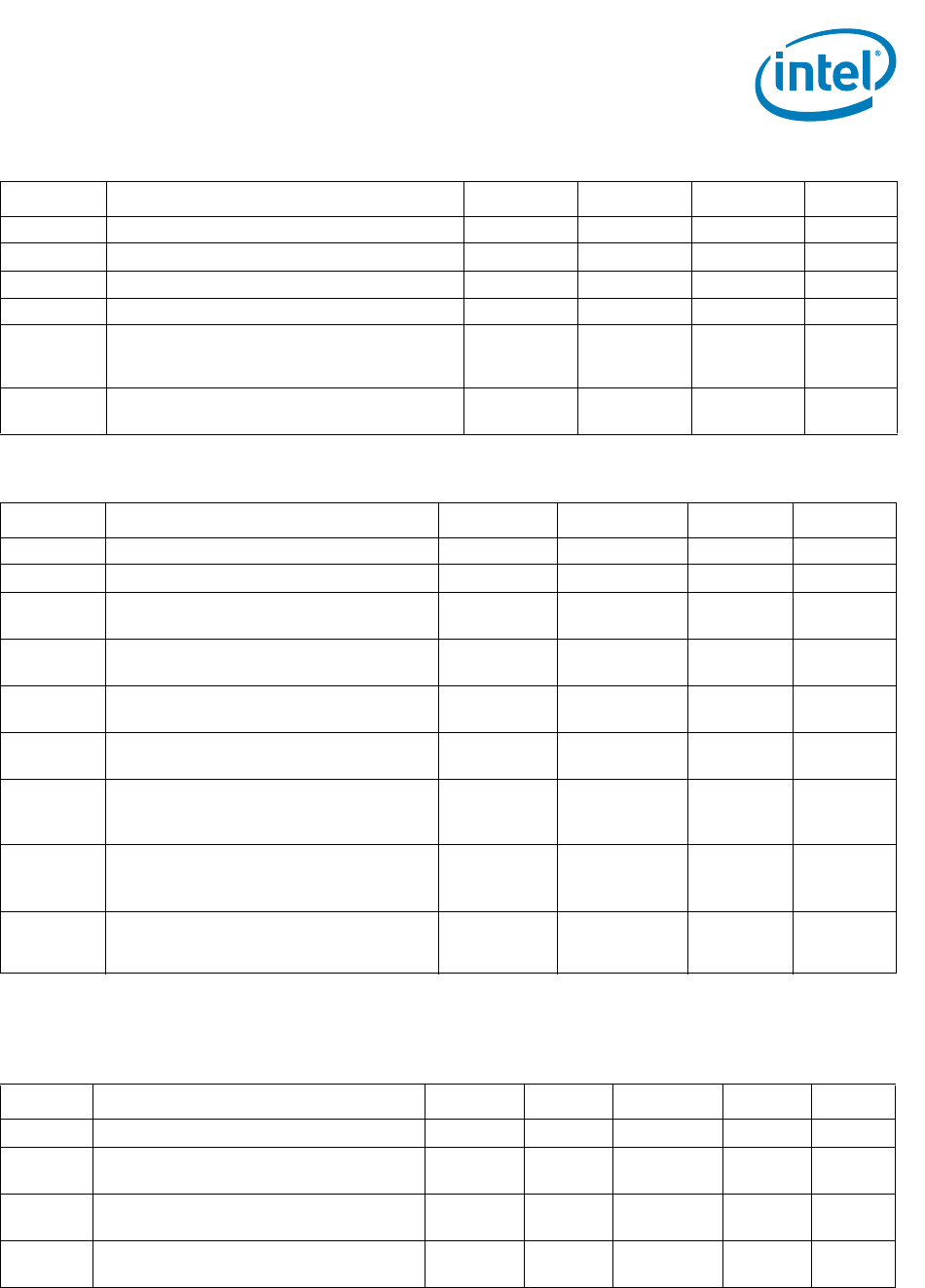

Table 7-20. JTAG and TAP Signals DC Specifications

Symbol Parameter Min Max Units Notes

V

IL

Input Low Voltage 0.3*V

TT

V

V

IH

Input High Voltage 0.7*V

TT

V

V

OL

Output Low Voltage

(R

TEST

= 500 ohm)

0.12*V

TT

V

V

OH

Output High Voltage

(R

TEST

= 500 ohm)

0.88*V

TT

V

R

ON

Buffer On Resistance

Signals BPM_N[7:0], TDO, EAR_N

14

Ω

I

IL

Input Leakage Current

Signals PREQ_N, TCK, TDI, TMS, TRST_N

-50 +50

μA

I

IL

Input Leakage Current

Signals BPM_N[7:0], TDO, EAR_N

(R

TEST

= 50 ohm)

+900

μA

I

O

Output Current

Signal PRDY_N

(R

TEST

= 500 ohm)

-1.50 +1.50 mA

Input Edge Rate

Signals: BPM_N[7:0], EAR_N, PREQ_N, TCK,

TDI, TMS, TRST_N

0.05 V/ns 1, 2

Table 7-21. Serial VID Interface (SVID) DC Specifications (Sheet 1 of 2)

Symbol Parameter Min Typ Max Units Notes

V

TT

CPU I/O Voltage VTT - 3% 1.05 VTT + 3% V

V

IL

Input Low Voltage

Signals SVIDDATA, SVIDALERT_N

0.3*V

TT

V1

V

IH

Input High Voltage

Signals SVIDDATA, SVIDALERT_N

0.7*V

TT

V1

V

OH

Output High Voltage

Signals SVIDCLK, SVIDDATA

V

TT(max)

V1

Table 7-19. SMBus DC Specifications (Sheet 2 of 2)

Symbol Parameter Min Max Units Notes