Intel® Xeon® Processor E5-1600/E5-2600/E5-4600 Product Families 183

Datasheet Volume One

7.9 Signal Quality

Data transfer requires the clean reception of data signals and clock signals. Ringing

below receiver thresholds, non-monotonic signal edges, and excessive voltage swings

will adversely affect system timings. Ringback and signal non-monotonicity cannot be

tolerated since these phenomena may inadvertently advance receiver state machines.

Excessive signal swings (overshoot and undershoot) are detrimental to silicon gate

oxide integrity, and can cause device failure if absolute voltage limits are exceeded.

Overshoot and undershoot can also cause timing degradation due to the build up of

inter-symbol interference (ISI) effects.

For these reasons, it is crucial that the designer work towards a solution that provides

acceptable signal quality across all systematic variations encountered in volume

manufacturing.

This section documents signal quality metrics used to derive topology and routing

guidelines through simulation. All specifications are specified at the processor die (pad

measurements).

Specifications for signal quality are for measurements at the processor core only and

are only observable through simulation. Therefore, proper simulation is the only way to

verify proper timing and signal quality.

7.9.1 DDR3 Signal Quality Specifications

Various scenarios for the DDR3 Signals have been simulated to generate a set of layout

guidelines which are available in the appropriate Platform Design Guide (PDG).

Overshoot (or undershoot) is the absolute value of the maximum voltage above or

below V

SS

. The overshoot/undershoot specifications limit transitions beyond specified

maximum voltages or V

SS

due to the fast signal edge rates. The processor can be

damaged by single and/or repeated overshoot or undershoot events on any input,

output, or I/O buffer if the charge is large enough (i.e., if the over/undershoot is great

enough). Baseboard designs which meet signal integrity and timing requirements and

which do not exceed the maximum overshoot or undershoot limits listed in Table 7-24

will insure reliable IO performance for the lifetime of the processor.

7.9.2 I/O Signal Quality Specifications

Signal Quality specifications for PCIe* Signals are included as part of the PCIe* DC

specifications. Various scenarios have been simulated to generate a set of layout

guidelines which are available in the appropriate Platform Design Guide (PDG).

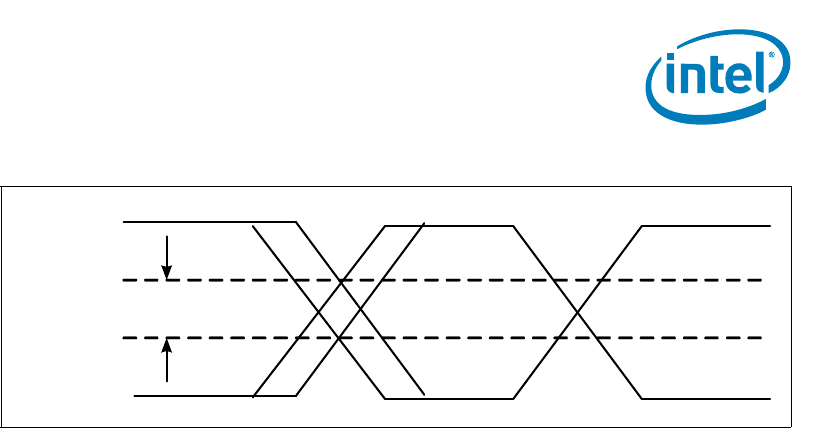

Figure 7-10. BCLK{0/1} Single Ended Clock Measurement Points for Delta Cross Point

V

CROSS DELTA

= 140 mV

BCLK_DN

BCLK_DP