Intel® Server Board SE7320SP2 & Intel Server Board SE7525GP2 TPS Functional Architecture

Revision 2.0

65

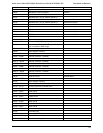

Address (es) Resource Notes

03BCh – 03BFh Parallel Port 1 (Primary)

03C0h – 03CFh Video Display Controller

03D4h – 03Dah Color Graphics Controller

03E8h – 03Efh Serial Port A

03F0h – 03F5h Floppy Disk Controller

03F6h – 03F7h Primary IDE – Sec Floppy

03F8h – 03FFh Serial Port A (primary)

0400h – 043Fh DMA Controller 1, Extended Mode Registers

0461h Extended NMI / Reset Control

0480h – 048Fh DMA High Page Register

04C0h – 04CFh DMA Controller 2, High Base Register

04D0h – 04D1h Interrupt Controllers 1 and 2 Control Register

04D4h – 04D7h DMA Controller 2, Extended Mode Register

04D8h – 04DFh Reserved

04E0h – 04FFh DMA Channel Stop Registers

051Ch Software NMI (051Ch)

0678h – 067Ah Parallel Port (ECP)

0778h – 077Ah Parallel Port (ECP)

07BCh – 07Beh Parallel Port (ECP)

0CF8h PCI CONFIG_ADDRESS Register

0CF9h

Intel® Server Board SUNPRAIRIE Turbo and

Reset Control

0CFCh PCI CONFIG_DATA Register

3.7.3 Accessing Configuration Space

All PCI devices contain PCI configuration space, accessed using mechanism #1 defined in the

PCI Local Bus Specification. If dual processors are used, only the processor designated as the

Boot Strap Processor (BSP) should perform PCI configuration space accesses. Precautions

should be taken to guarantee that only one processor performs system configuration.

Two Dword I/O registers in the chipset are used for the configuration space register access:

• CONFIG_ADDRESS (I/O address 0CF8h)

• CONFIG_DATA (I/O address 0CFCh)

When CONFIG_ADDRESS is written to with a 32-bit value selecting the bus number, device on

the bus, and specific configuration register in the device, a subsequent read or write of

CONFIG_DATA initiates the data transfer to/from the selected configuration register. Byte

enables are valid during accesses to CONFIG_DATA; they determine whether the configuration

register is being accessed or not. Only full Dword reads and writes to CONFIG_ADDRESS are

recognized as a configuration access by the chipset. All other I/O accesses to

CONFIG_ADDRESS are treated as normal I/O transactions.